DCR3790B30(2009) View Datasheet(PDF) - Dynex Semiconductor

Part Name

Description

Manufacturer

DCR3790B30 Datasheet PDF : 10 Pages

| |||

SEMICONDUCTOR

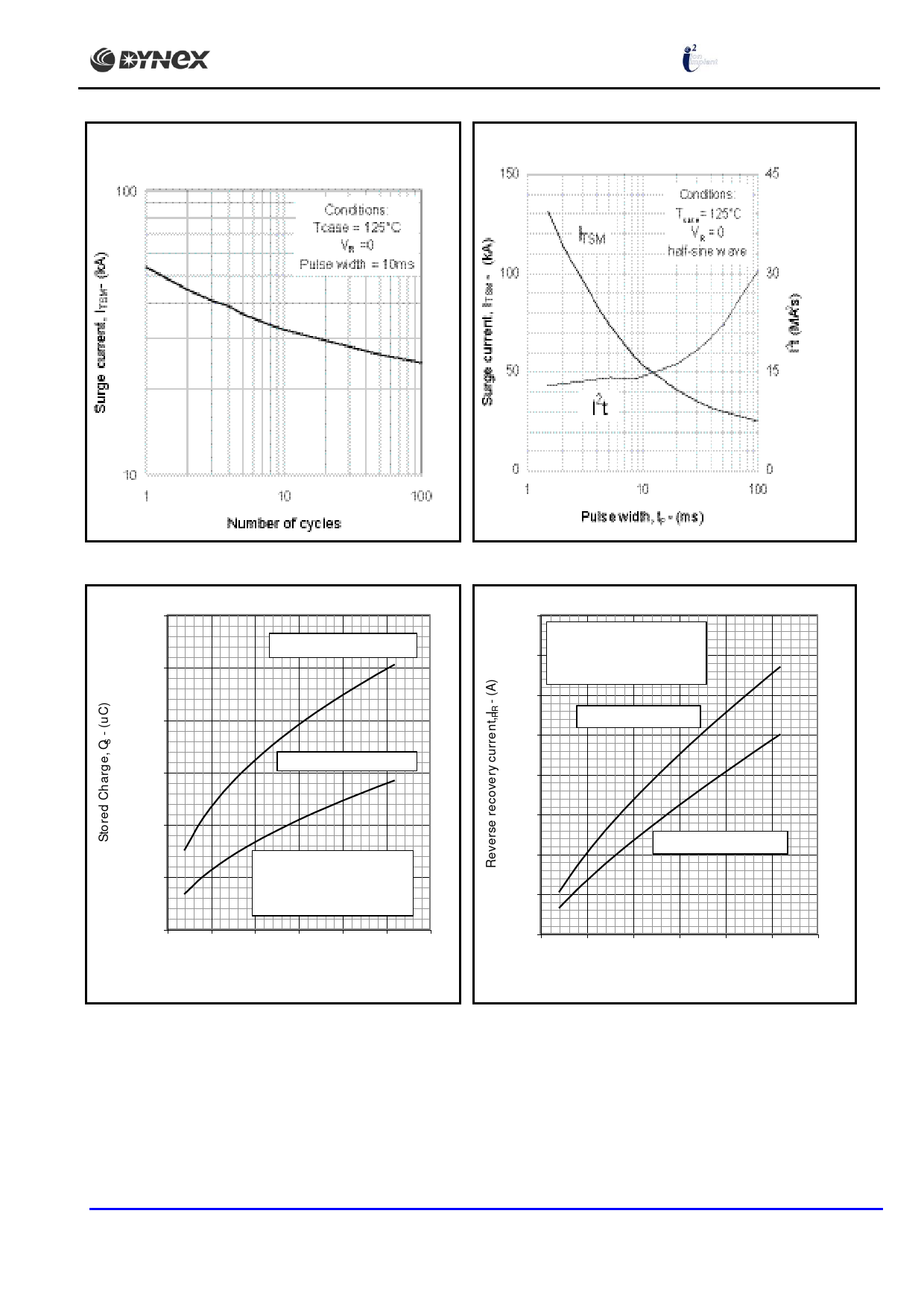

100

DCR3790B42

Conditions:

Tcase = 125°C

VR =0

Pulse width = 10ms

150

ITSM

100

45

Conditions:

Tcase= 125°C

VR = 0

half-sine w ave

30

10

1

10

100

Number of cycles

Fig.10 Multi-cycle surge current

30000

25000

Max QS = 5404.7*(di/dt)0.4733

20000

15000

Min QS = 2246.2*(di/dt)0.5657

10000

5000

Conditions:

Tj = 125ºC, VRpeak ~ 2500V,

VRM ~ 1700V

snubber as required to control reverse

voltages

0

0

5

10 15 20 25 30

Rate of decay of on-state current, di/dt - (A/us)

Fig.12 Stored charge

50

15

I2t

0

0

1

10

100

Pulse width, tP - (ms)

Fig.11 Single-cycle surge current

800

700

600

500

Conditions:

Tj = 125ºC, VRpeak ~ 2500V,

VRM ~ 1700V

snubber as required to control

reverse voltages

IRR max = 62.4*(di/dt)0.7284

400

300

200

IRR min = 36.417*(di/dt)0.8041

100

0

0

5

10

15

20

25

30

Rate of decay of on-state current, di/dt - (A/us)

Fig.13 Reverse recovery current

7/10

www.dynexsemi.com