MAX3991UTG View Datasheet(PDF) - Maxim Integrated

Part Name

Description

Manufacturer

MAX3991UTG Datasheet PDF : 12 Pages

| |||

10Gbps Clock and Data Recovery

with Limiting Amplifier

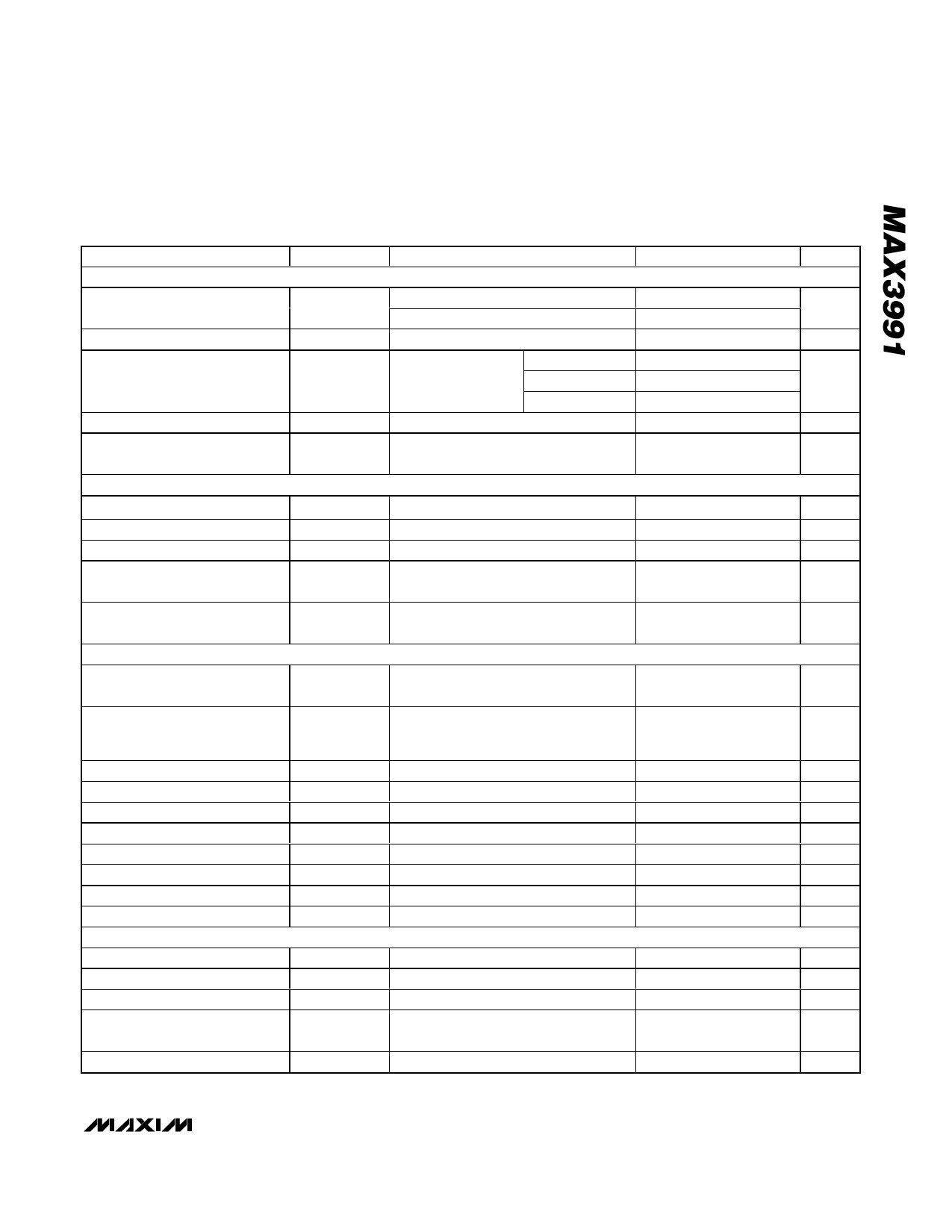

ELECTRICAL CHARACTERISTICS (continued)

(See Table 1 for operating conditions. Typical values at VCC = +3.3V, TA = +25°C, unless otherwise noted.)

PARAMETER

JITTER SPECIFICATION

Jitter Peaking

Jitter Transfer Bandwidth

Sinusoidal Jitter Tolerance

Jitter Generation

SYMBOL

CONDITIONS

120kHz < f ≤ 8MHz (Notes 2, 4)

JP

f ≤ 120kHz (Notes 2, 4)

JBW

(Notes 2, 4)

f = 400kHz

(Notes 2, 4, 6)

f = 4MHz

f = 80MHz

(Notes 2, 4, 7)

MIN TYP MAX

0.05 0.25

0.03

5.6

8.0

3.0 >3 (Note 5)

0.55 >0.6 (Note 5)

0.45 >0.5 (Note 5)

4.5 11.0

Serial Data Output Deterministic

Jitter

DJ

PRBS 27 - 1 (Note 2)

4.6

13

PLL ACQUISITION/LOCK SPECIFICATION

Acquisition Time

Figures 1, 2 (Note 2)

200

LOL Assert Time

Maximum Frequency Pullin Time

Figure 1 (Note 2)

(Note 8)

90

2

Frequency Difference at which

LOL is Asserted

∆f/fREFCLK

∆f = |fVCO / N - fREFCLK|,

N = 16 or 64

651

Frequency Difference at which

LOL is DeAsserted

∆f/fREFCLK

∆f = |fVCO / N - fREFCLK|,

N = 16 or 64

500

LOSS-OF-SIGNAL (LOS) SPECIFICATION

UNITS

dB

MHz

UIP-P

mUIRMS

psP-P

µs

µs

ms

ppm

ppm

VTH Control Voltage Range

VTH

150

500

mV

LOS Gain Factor

VTH/

VLOS_ASSERT

10

V/V

Minimum LOS Assert Voltage

Maximum LOS Assert Voltage

LOS Gain-Factor Accuracy

VLOS_ASSERT

VLOS_ASSERT

(Notes 2, 9)

15

mV

50

mV

-1.5

+1.5

dB

LOS Hysteresis

(Notes 2, 10)

3.5

3.7

3.9

dB

LOS Gain-Factor Stability

(Note 2) Overtemperature and supply

-10

+10

%

LOS Assert Time

Figure 2 (Note 2)

3

90

µs

LOS Deassert Time

Figure 2 (Note 2)

90

µs

VTH Input Current

-5

+5

µA

LVTTL INPUT/OUTPUT SPECIFICATION (LOL, LOS, FCTL1, FCTL2)

Input High Voltage

VIH

Input Low Voltage

VIL

Input Current

2.0

V

0.8

V

-30

+30

µA

Output High Voltage

VOH

Sourcing 30µA

VCC -

0.5

V

Output Low Voltage

VOL

Sinking 1mA

0.4

V

_______________________________________________________________________________________ 3