C32025 View Datasheet(PDF) - Unspecified

Part Name

Description

Manufacturer

C32025 Datasheet PDF : 9 Pages

| |||

C32025 Megafunction Datasheet

Phase Generator

Internal clock cycle divider. Machine cycle consists of four main clock cycles.

Reset Control

Reset input is sampled once a machine cycle and distributed all over the core.

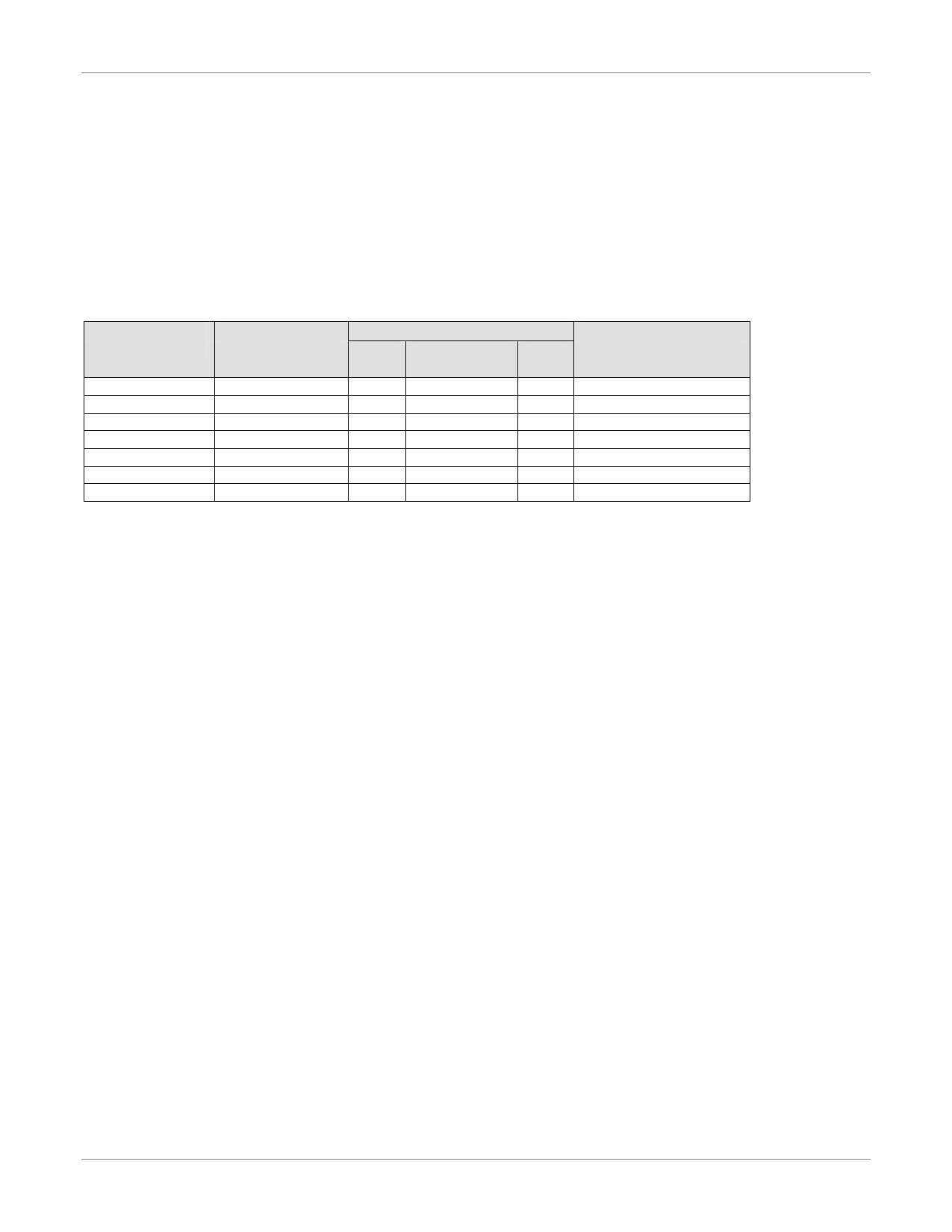

Device Utilization & Performance

Supported

Family

Device

Tested

Utilization

LEs

Memory

DSP

Performance

Fmax

Flex²

Acex²

Apex¹

Apex2¹

Cyclone¹

Stratix¹

Startix2¹

EPF10K100E-1

EP1K100E-1

EP20K200E-1

EP2A15-7

EP1C6-6

EP1S10-5

EP2S15-3

4532

4532

4420

4528

4066

4370

3835

M4Ks; 1 M512

M4Ks; 1 M512

19 ESBs

19 ESBs

37 ESBs

7 EABs

7 EABs

Notes:

1.

2.

Implemented with 544x16 bit RAM and 4096 x 16 bit ROM

Implemented with 544x16 bit RAM and 1048 x 16 bit ROM

Core Assumptions

The IACK_N and MSC_N lines are valid only

during the quarter-phases Q1 and Q2 (when

CLKOUT1 = 0). In other cases their behaviour is

unpredictable in the original Texas Instruments

TMS320C25 device. The C32025 sets them to 1s

in Q3 and Q4, except in the hold mode when

MSC_N remains 0.

The original Texas Instruments TMS320C25 serial

port doesn't re-start properly when a frame sync

pulse occurs in the middle of a transmission. The

new transfer following a re-start is interrupted in

a moment when previous transmission should be

completed as if and there were no frame sync

pulses, but the transferred data is re-loaded. The

C32025 serial interface works properly as it is

described in the specification document.

The CLKR and CLKX inputs are clock inputs in the

original Texas Instruments TMS320C25 serial

port registers. In C32025 they are not clock

signals but are synchronously sampled at every

positive edge of the main clock signal. The same

applies to the external interrupts inputs INT0_N,

INT1_N and INT2_N. They are connected to a

negative edge flip-flop in the original device, but

in C32025 they are sampled synchronously with

1

24 MHz

1

26 MHZ

-

37 MHz

-

65 MHz

-

95 MHz

-

101 MHz

-

130 MHz

main clock signal. These changes cause delays in

the serial port operation and forces the minimum

length of an external interrupt pulse to at least

one oscillator cycle.

Some registers are not reset by RS_N in the

original Texas Instruments TMS320C25 device,

but are reset in the C32025. They are:

ACC 00000000h

PR 00000000h

TR 0000h

ARP 000

ARB 000

DP 000000000

IMR 000000

DRR

0000h

DXR

0000h

Stack

all levels are reset to 0000h

OVM

0

TC

0

AR0-AR7 all registers are reset to 0000h

CAST, Inc.

Page 7