71215S10 View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

71215S10

71215S10 Datasheet PDF : 14 Pages

| |||

IDT71215

BiCMOS 16Kx15 CACHE-TAG RAM

COMMERCIAL TEMPERATURE RANGE

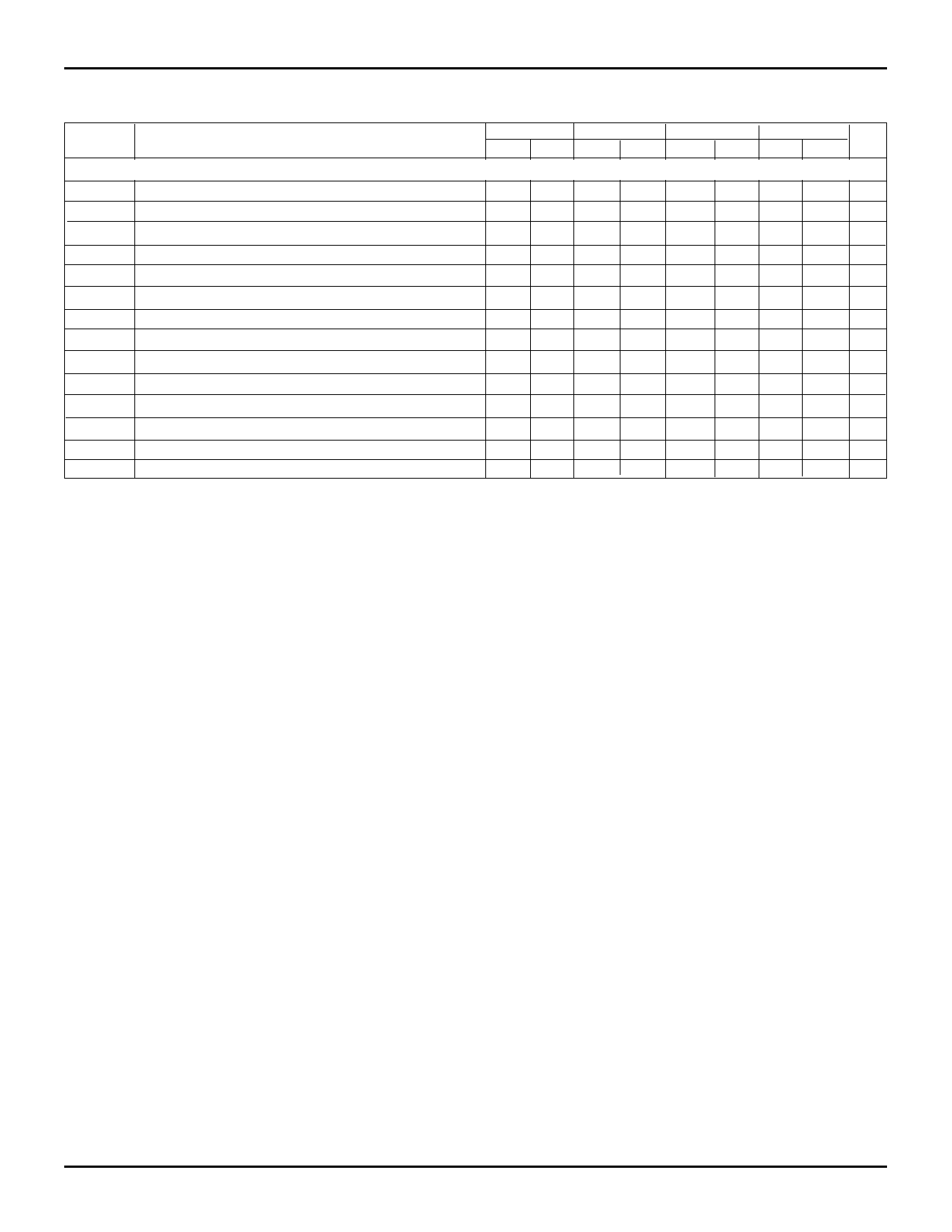

AC ELECTRICAL CHARACTERISTICS (1)

(VCC = 5.0V ± 5%, VCCQ = 5.0V ± 5% OR 3.3V ± 0.3V, TA = 0 to 70°C)

IDT71215S8 IDT71215S9 IDT71215S10 IDT71215S12

Symbol

Parameter

Min. Max. Min. Max. Min. Max. Min. Max. Unit

Write Cycle and Clock Parameters

tCYC

Clock Cycle Time

15 — 15 — 15

— 16.6 — ns

tCH(2, 3)

Clock Pulse HIGH

4.5 — 4.5 — 4.5

—

5

— ns

tCL(2, 3)

Clock Pulse LOW

4.5 — 4.5 — 4.5

—

5

— ns

tS

WET, WES, Chip Select, and Input Data Set-up Time

3

—

3—

3

—

3

— ns

tH

WET, WES, Chip Select, and Input Data Hold Time

1

—

1—

1

—

1

— ns

tSA

Address Set-up Time

3

—

3—

3

—

3

— ns

tHA

Address Hold Time

1

—

1—

1

—

1

— ns

tWMI

CLK HIGH Write to MATCH and BRDY Invalid

— 6 —7 —

7 — 8 ns

tCKLZ(3) CLK HIGH Read to Outputs in Low-Z

1.5 — 1.5 — 1.5 — 1.5 — ns

tCTV(4)

CLK HIGH Read to Tag Bits Valid

—

9

— 10 —

10 — 12 ns

tCSV(4)

CLK HIGH Write to Status Outputs Valid

— 8 —9 —

9 — 10 ns

tCSH(3)

Status Output Hold from CLK HIGH Write

0

—

0—

0

— 0 — ns

tWHPL

WET and WES HIGH to PWRDN LOW

5

—

5—

5

—

5

— ns

tPUWL

PWRDN HIGH to WET and WES Active

50 — 50 — 50

NOTES:

1. All Write cycles are synchronous and referenced from rising CLK.

2. This parameter is measured as a HIGH time above 2.0V and a LOW time below 0.8V.

3. This parameter is guaranteed with the AC Load (Figure 3) by device characterization, but is not production tested.

4. Addresses are stable prior to CLK transition HIGH.

— 50 — ns

3075 tbl 14

14.3

8