SI3012-KT View Datasheet(PDF) - Silicon Laboratories

Part Name

Description

Manufacturer

SI3012-KT Datasheet PDF : 64 Pages

| |||

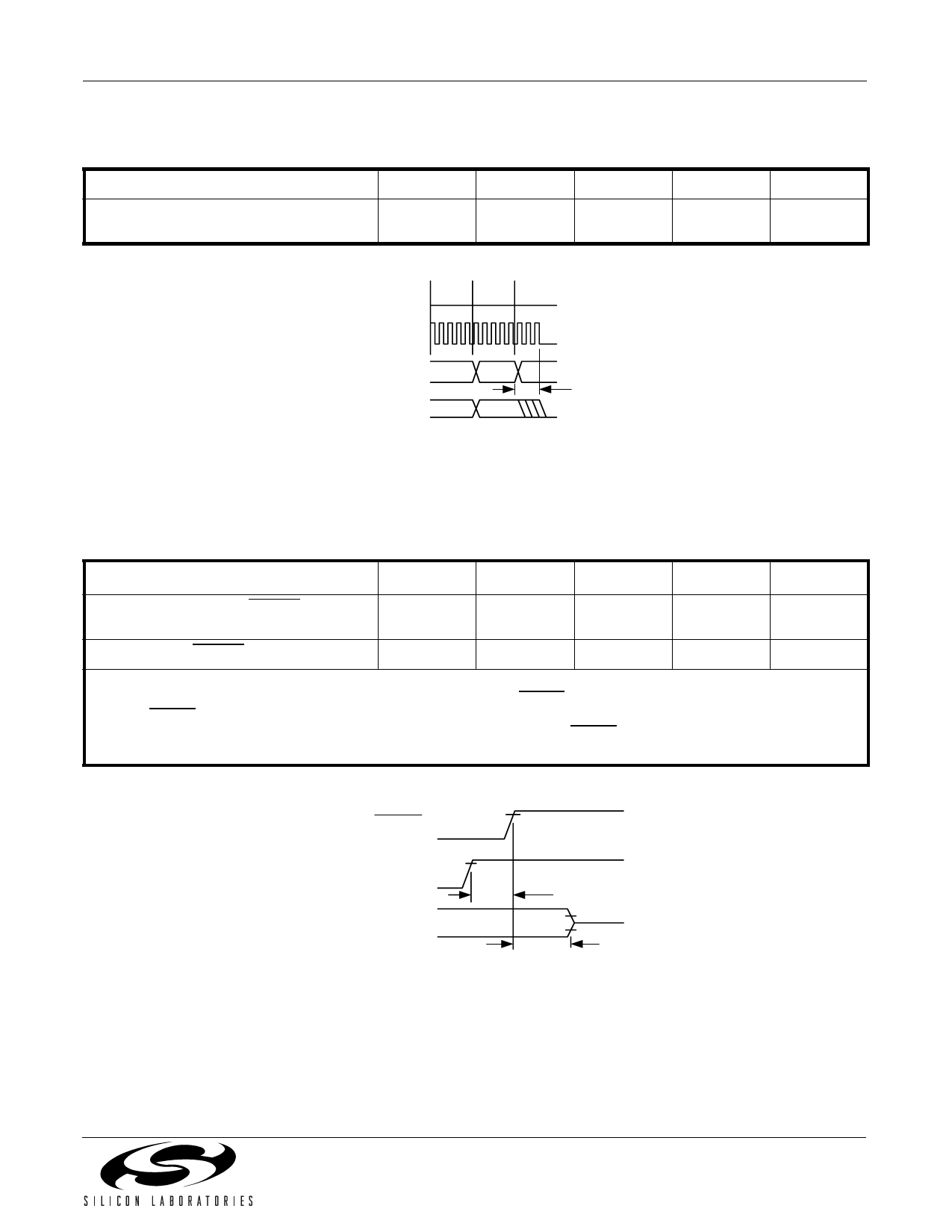

Table 12. AC Link Timing Characteristics— Low Power Mode Timing

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter

Symbol

Min

Typ

End of Slot 2 to BIT_CLK, SDATA_IN

Ts2_pdown

—

—

Low

Si3038

Max

Unit

1.0

µs

SYNC Slot 1 Slot 2

BIT_CLK

SDATA_OUT

W rite to

0x56

Data

MLNK

SDATA_IN

Don't care

Ts2_pdown

Note: BIT_CLK not to scale

Figure 7. AC-Link Low Power Mode Timing Diagram

Table 13. ATE Test Mode

(VD = 3.0 to 3.6 V, VA = Charge Pump, TA = 25°C, CL = 50 pF)

Parameter1,2

Symbol

Min

Typ

Max

Unit

Setup to rising edge of RESET (also

Tsetup2rst

15.0

—

—

ns

applies to SYNC)

Rising edge of RESET to Hi-Z delay

Toff

—

—

25.0

ns

Notes:

1. All AC link signals are normally low through the trailing edge of RESET. Bringing SDATA_OUT high for the trailing edge

of RESET causes AC’97 AC-link outputs to go high impedance, which is suitable for ATE in circuit testing.

2. When the test mode has been entered, AC’97 must be issued another RESET with all AC-link signals low to return to

the normal operating mode.

RESET

SDATA_OUT

SDATA_IN, BIT_CLK

T off

T setup2rst

H i-Z

Figure 8. ATE Test Mode Timing Diagram

Rev. 2.01

11