A8351601 View Datasheet(PDF) - AMIC Technology

Part Name

Description

Manufacturer

A8351601 Datasheet PDF : 44 Pages

| |||

A8351601 Series

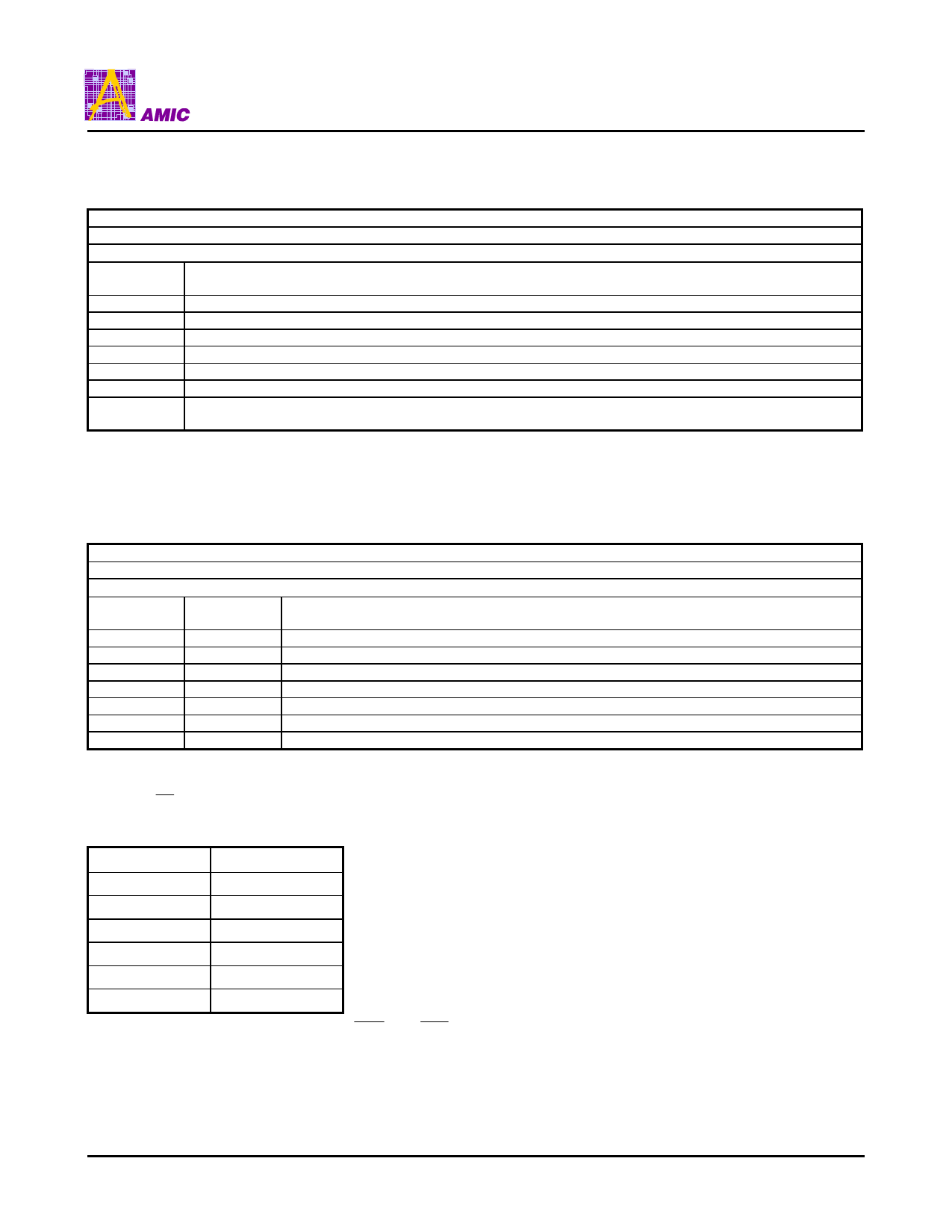

PCON:

Power Control Register. Not Bit Addressable.

7

6

5

4

3

2

1

0

SMOD

-

-

-

GF1

GF0

PD

IDL

Register Description:

SMOD

Double baud rate bit. If Timer 1 is used to generate baud rate and SMOD=1, the baud rate is doubled when

the serial port is used in modes 1, 2, or 3.

-

Not implemented, reserve for future use. (1)

-

Not implemented, reserve for future use. (1)

-

Not implemented, reserve for future use. (1)

GF1

General purpose flag bit.

GF0

General purpose flag bit.

PD

Power-down bit. Setting this bit activates power-down operation in the A8351601.

IDL

Idle mode bit. Setting this bit activates idle mode operation in the A8351601. If 1s are written to PD and IDL

at the same time, PD takes precedence.

Note:

1. User software should not write 1s to reserved bits. These bits may be used in future products to invoke new features.

IE

Interrupt Enable Register. Bit Addressable.

7

6

EA

-

Register Description:

EA

IE.7

-

IE.6

ET2

IE.5

ES

IE.4

ET1

IE.3

EX1

IE.2

ET0

IE.1

EX0

IE.0

5

4

3

2

1

0

ET2

ES

ET1

EX1

ET0

EX0

Disable all interrupts. If EA=0, no interrupt will be acknowledged. If EA=1, each interrupt

source is individually enabled or disabled by setting or clearing its enable bit.

Not implemented, reserve for future use. (5)

Enables or disables timer 2 overflow interrupt.

Enable or disable the serial port interrupt.

Enable or disable the timer 1 overflow interrupt.

EX1 IE.2 Enable or disable external interrupt 1.

Enable or disable the timer 0 overflow interrupt.

Enable or disable external interrupt 0.

Note:

To use any of the interrupts in the 80C51 Family, the following three steps must be taken:

1. Set the EA (enable all) bit in the IE register to 1.

2. Set the corresponding individual interrupt enable bit in the IE register to 1.

3. Begin the interrupt service routine at the corresponding Vector Address of that interrupt (see below).

Interrupt Source Vector Address

IE0

0003H

TF0

000BH

IE1

0013H

TF1

001BH

RI & TI

0023H

TF2 and EXF2

002BH

4. In addition, for external interrupts, pins INT0 and INT1 (P3.2 and P3.3) must be set to 1, and depending on whether the

interrupt is to be level or transition activated, bits IT0 or IT1 in the TCON register may need to be set to 0 or 1.

ITX = 0 level activated (X = 0, 1)

ITX = 1 transition activated

5. User software should not write 1s to reserved bits. These bits may be used in future products to invoke new features.

(July, 2002, Version 1.0)

8

AMIC Technology, Inc.