AD7150BRMZ-REEL(Rev0) View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

AD7150BRMZ-REEL

(Rev.:Rev0)

(Rev.:Rev0)

AD7150BRMZ-REEL Datasheet PDF : 28 Pages

| |||

AD7150

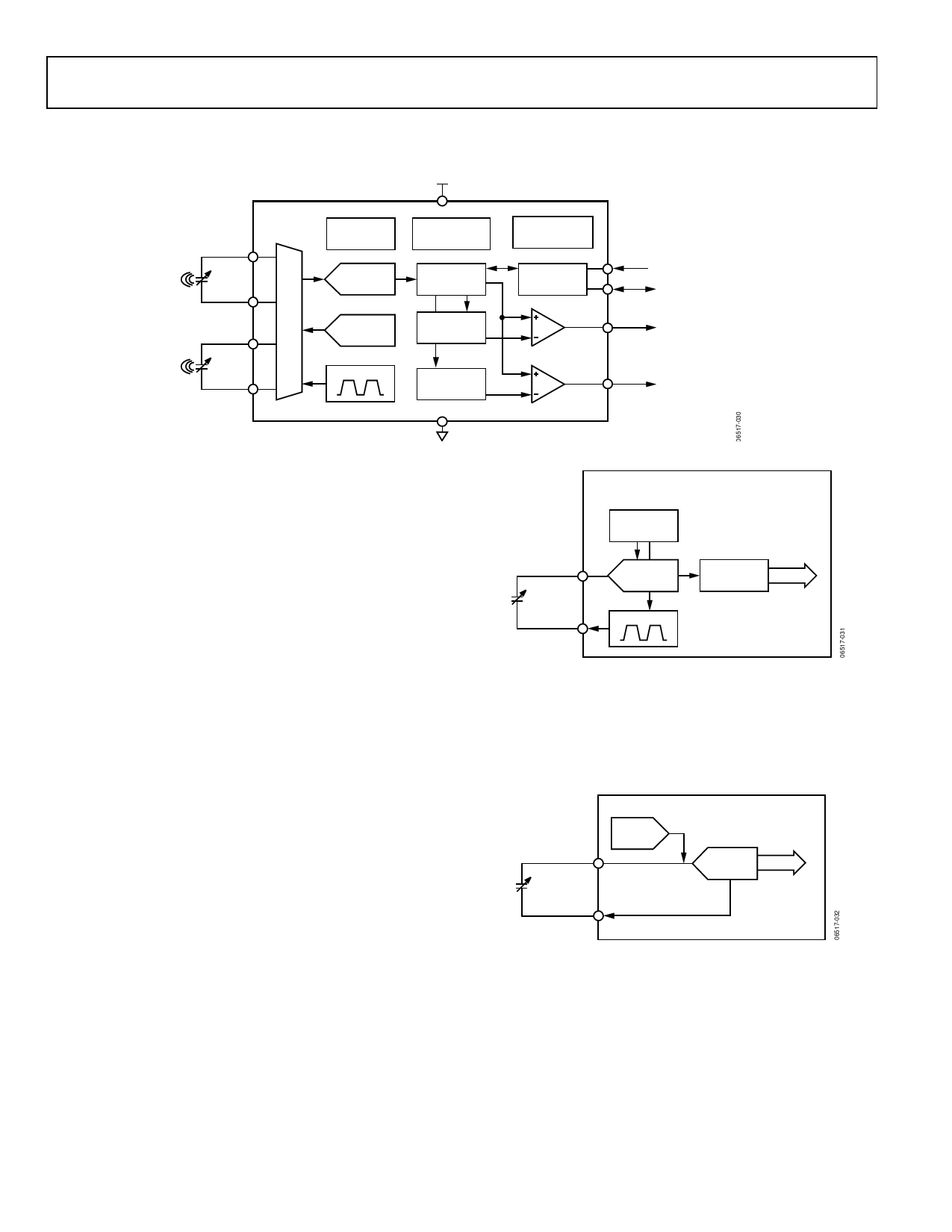

ARCHITECTURE AND MAIN FEATURES

CIN1

AD7150

CLOCK

GENERATOR

CX1

EXC1

CIN2

MUX

Σ-Δ CDC

CAPDAC

CX2

EXC2

EXCITATION

3.3V

VDD

POWER-DOWN

TIMER

DIGITAL

FILTER

THRESHOLD

THRESHOLD

POWER SUPPLY

MONITOR

SERIAL

INTERFACE

SCL

PROGRAMMING

SDA INTERFACE

OUT1

DIGITAL

OUTPUTS

OUT2

GND

Figure 22. AD7150 Block Diagram

The AD7150 core is a high performance capacitance-to-digital

converter (CDC) that allows the part to be interfaced directly to

a capacitive sensor.

The comparators compare the CDC result with thresholds, either

fixed or dynamically adjusted by the on-chip adaptive threshold

algorithm engine. Thus, the outputs indicate a defined change in

the input sensor capacitance.

The AD7150 also integrates an excitation source and CAPDAC

for the capacitive inputs, an input multiplexer, a complete clock

generator, a power-down timer, a power supply monitor, control

logic, and an I2C®-compatible serial interface for configuring the

part and accessing the internal CDC data and status, if required

in the system (see Figure 22).

CAPACITANCE-TO-DIGITAL CONVERTER

Figure 23 shows the CDC simplified functional diagram. The

converter consists of a second-order sigma delta (Σ-Δ), charge

balancing modulator and a third-order digital filter. The

measured capacitance CX is connected between an excitation

source and the Σ-Δ modulator input. The excitation signal is

applied on the CX during the conversion, and the modulator

continuously samples the charge going through the CX. The

digital filter processes the modulator output, which is a stream

of 0s and 1s containing the information in 0 and 1 density. The data

is processed by the adaptive threshold engine and output compara-

tors; the data can be also read through the serial interface.

The AD7150 is designed for floating capacitive sensors.

Therefore, both CX plates have to be isolated from ground or

any other fixed potential node in the system.

The AD7150 features slew rate limiting on the excitation voltage

output, which decreases the energy of higher harmonics on the

excitation signal and dramatically improves the system

electromagnetic compatibility (EMC).

CIN

CX

0pF TO 4pF

EXC

CAPACITANCE TO DIGITAL CONVERTER

(CDC)

CLOCK

GENERATOR

Σ-Δ

MODULATOR

0x000 TO 0xFFF

DATA

DIGITAL

FILTER

EXCITATION

Figure 23. CDC Simplified Block Diagram

CAPDAC

The AD7150 CDC core maximum full-scale input range is 4 pF.

However, the part can accept a higher capacitance on the input,

and the offset (nonchanging component) capacitance of up to 10

pF can be balanced by a programmable on-chip CAPDAC.

CAPDAC

10pF

CIN

CX

10pF TO 14pF

EXC

0x000 TO 0xFFF

DATA

0pF TO 4pF

Figure 24. Using CAPDAC

The CAPDAC can be understood as a negative capacitance

connected internally to the CIN pin. The CAPDAC has a 6-bit

resolution and a monotonic transfer function. Figure 24 shows

how to use the CAPDAC to shift the CDC 4 pF input range to

measure capacitance between 10 pF and 14 pF.

Rev. 0 | Page 10 of 28