AD9139(Rev0) View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

AD9139 Datasheet PDF : 56 Pages

| |||

AD9139

Data Sheet

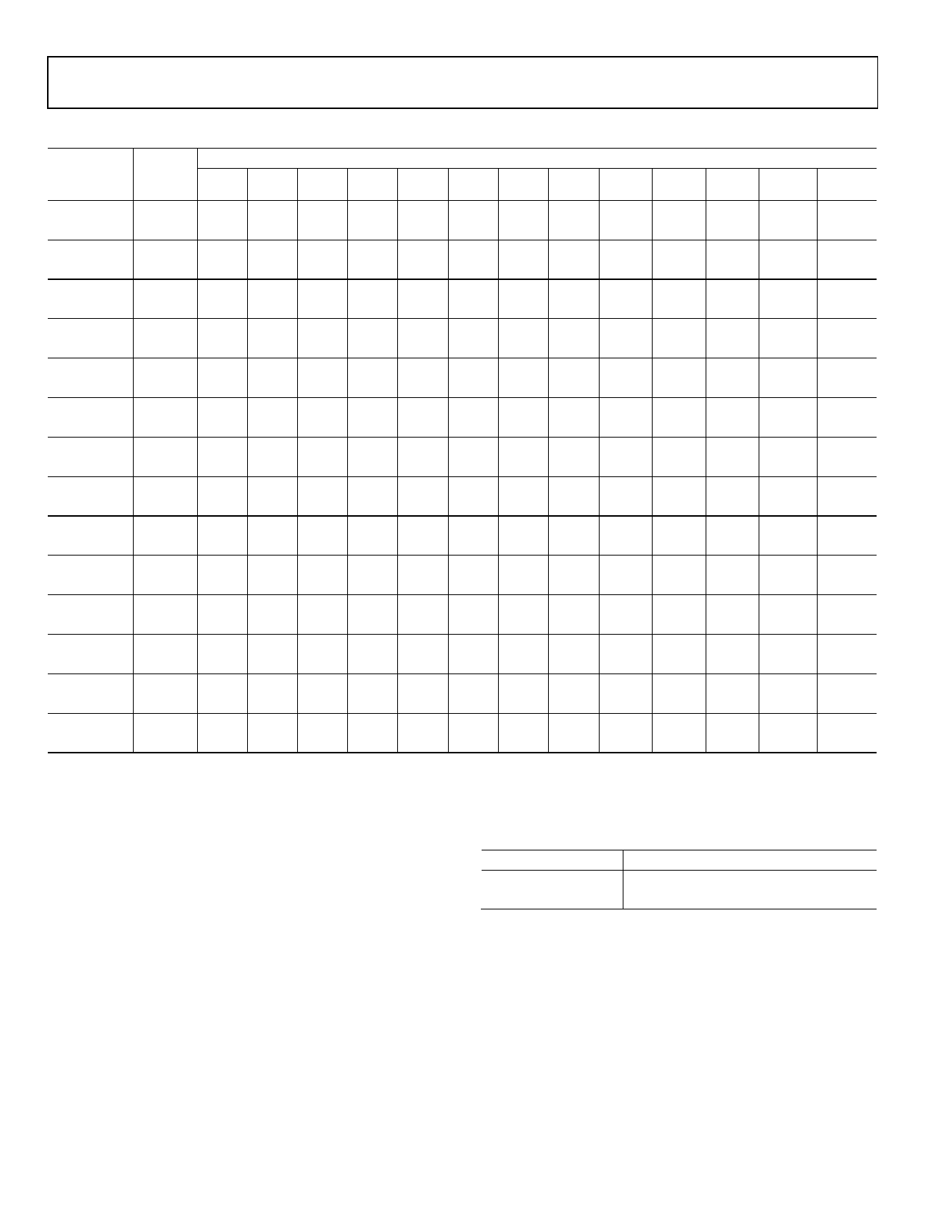

Table 13. DLL Phase Setup and Hold Times (Typical)

Frequency,

Data Port Setup and Hold Times (ps) at DLL Phase

fDCI1

Time

(MHz)

(ps)

−6 −5 −4 −3 −2 −1 0

+1 +2

+3

250

tS

−93 −196 −312 −416 −530 −658 −770 −878 −983 −1093

tH

468 579 707 825 947 1067 1188 1315 1442 1570

275

tS

−87 −172 −264 −364 −464 −556 −653 −756 −859 −956

tH

451 537 646 757 878 977 1092 1218 1311 1423

300

tS

−82 −166 −256 −341 −426 −515 −622 −715 −809 −900

tH

422 500 598 703 803 897 1000 1105 1203 1303

325

tS

−46 −114 −190 −271 −358 −447 −538 −612 −706 −806

tH

405 483 563 647 740 832 914 1000 1100 1200

350

tS

−23 −92 −180 −252 −328 −409 −491 −574 −654 −731

tH

383 451 524 607 682 762 844 930 1011 1097

375

tS

−7 −82 −150 −225 −315 −391 −461 −526 −595 −661

tH

401 466 504 569 641 718 783 863 941 1025

400

tS

−46 −98 −161 −243 −303 −384 −448 −513 −578 −643

tH

385 445 503 546 604 674 748 826 890 965

425

tS

4

−52 −110 −170 −229 −297 −394 −449 −517 −579

tH

358 408 465 524 595 625 692 762 829 900

450

tS

11

−34 −92 −147 −209 −269 −324 −386 −446 −509

tH

354 406 457 516 573 637 693 731 792 852

475

tS

−15 −51 −95 −147 −198 −255 −313 −366 −425 −480

tH

355 399 451 499 556 613 675 727 779 815

500

tS

9

−28 −77 −128 −183 −233 −288 −333 −390 −438

tH

313 354 399 445 500 555 615 668 726 783

525

tS

−7 −52 −100 −147 −187 −237 −285 −335 −387 −436

tH

311 356 395 438 489 537 592 645 692 746

550

tS

−5 −39 −74 −107 −147 −192 −249 −302 −352 −397

tH

300 340 378 423 468 510 560 610 659 710

575

tS

8

−28 −66 −102 −143 −181 −245 −280 −336 −366

tH

312 348 379 414 453 496 544 599 654 708

+4

−1193

1697

−1053

1537

−1001

1411

−891

1292

−819

1186

−726

1106

−713

1039

−641

966

−564

917

−530

873

−495

825

−483

799

−440

756

−406

759

+5

−1289

1777

−1151

1653

−1097

1522

−966

1380

−889

1277

−786

1187

−771

1110

−704

1032

−622

983

−585

930

−545

881

−530

850

−486

810

−443

806

+6

−1412

1876

−1251

1728

−1184

1612

−1044

1476

−959

1358

−853

1264

−833

1178

−752

1097

−672

1042

−640

988

−594

934

−581

909

−529

865

−488

847

1 Table 13 shows characterization data for selected fDCI frequencies. Other frequencies are possible; use Table 13 to estimate performance.

Table 13 shows the typical times for various DCI clock frequencies

that are required to calculate the data valid margin. Use Table 13 to

Register 0x0D optimizes the DLL stability over the operating

frequency range. Table 14 shows the recommended settings.

determine the amount of margin that is available for tuning of

the DSC sampling point.

Table 14. DLL Configuration Options

DCI Speed

Register 0x0D

Maximizing the opening of the eye in both the DCI and data

≥350 MHz

0x06

signals improves the reliability of the data port interface. Use

<350 MHz

0x86

differential controlled impedance traces of equal length (that is,

delay) between the host processor and the AD9139 input. To

Poll the status of the DLL by reading the data status register at

ensure coincident transitions with the data bits, implement the

Address 0x0E. Bit 0 indicates that the DLL is running and

DCI signal as an additional data line with an alternating

attempting lock; Bit 7 is 1 when the DLL has locked. Bit 2 is 1

(010101…) bit sequence from the same output drivers that are

when a valid data clock input (DCI) is detected. The warning

used for the data.

bits in [6:4] in Register 0x0E can be used as indicators that the

The DCI signal is ac-coupled by default; thus, removing the

DCI signal may cause DAC output chatter due to randomness

on the DCI input. To avoid this, disable the DAC output

whenever the DCI signal is not present by setting the DAC output

current power-down bit in Register 0x01[7] to 1. When the DCI

DAC may be operating in a nonideal location in the delay line.

Note that these bits are read at the SPI port speed, which is

much slower than the actual speed of the DLL. This means they

can only show a snapshot of what is happening as opposed to

giving real-time feedback.

signal is again present, enable the DAC output by programming

Register 0x01[7] to 0.

Rev. 0 | Page 20 of 56