ADF7023-J View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADF7023-J Datasheet PDF : 100 Pages

| |||

ADF7023-J

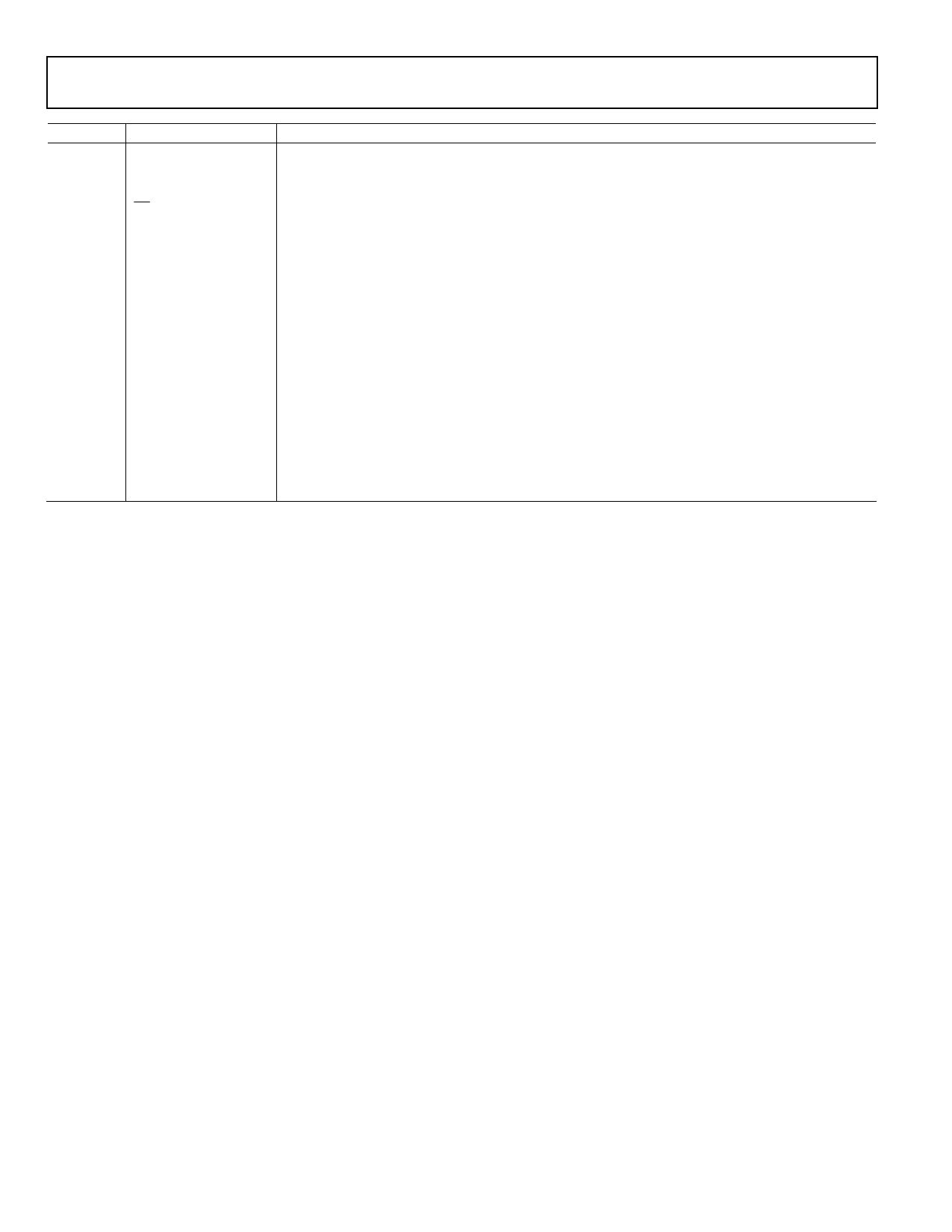

Pin No.

21

22

23

24

25

26

27

28

29

30

31

32

Mnemonic

MISO

SCLK

MOSI

CS

GP4

CREGDIG2

XOSC32KP_GP5_ATB1

XOSC32KN_ATB2

VDDBAT1

ADCIN_ATB3

ATB4

ADCVREF

EPAD

Description

Serial Port Master In/Slave Out.

Serial Port Clock.

Serial Port Master Out/Slave In.

Chip Select (Active Low). A pull-up resistor of 100 kΩ to VDD is recommended to prevent the host

processor from inadvertently waking the ADF7023-J from sleep.

Digital GPIO Test Pin 4.

Regulator Voltage for Digital Section of the Chip. A 220 nF capacitor should be placed between this

pin and ground for regulator stability and noise rejection.

Digital GPIO Test Pin 5. A 32 kHz watch crystal can be connected between this pin and

XOSC32KN_ATB2. Analog Test Pin 1.

A 32 kHz watch crystal can be connected between this pin and XOSC32KP_GP5_ATB1. Analog Test

Pin 2.

Digital Power Supply Pin One. Decoupling capacitors to the ground plane should be placed as close

as possible to this pin.

Analog-to-Digital Converter Input. Can be configured as an external PA enable signal. Analog Test

Pin 3.

Analog Test Pin 4. Can be configured as an external LNA enable signal.

ADC Reference Output. A 220 nF capacitor should be placed between this pin and ground for

adequate noise rejection.

The exposed package paddle must be connected to GND.

Rev. 0 | Page 18 of 100