ADM1021 View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADM1021 Datasheet PDF : 12 Pages

| |||

ADM1021

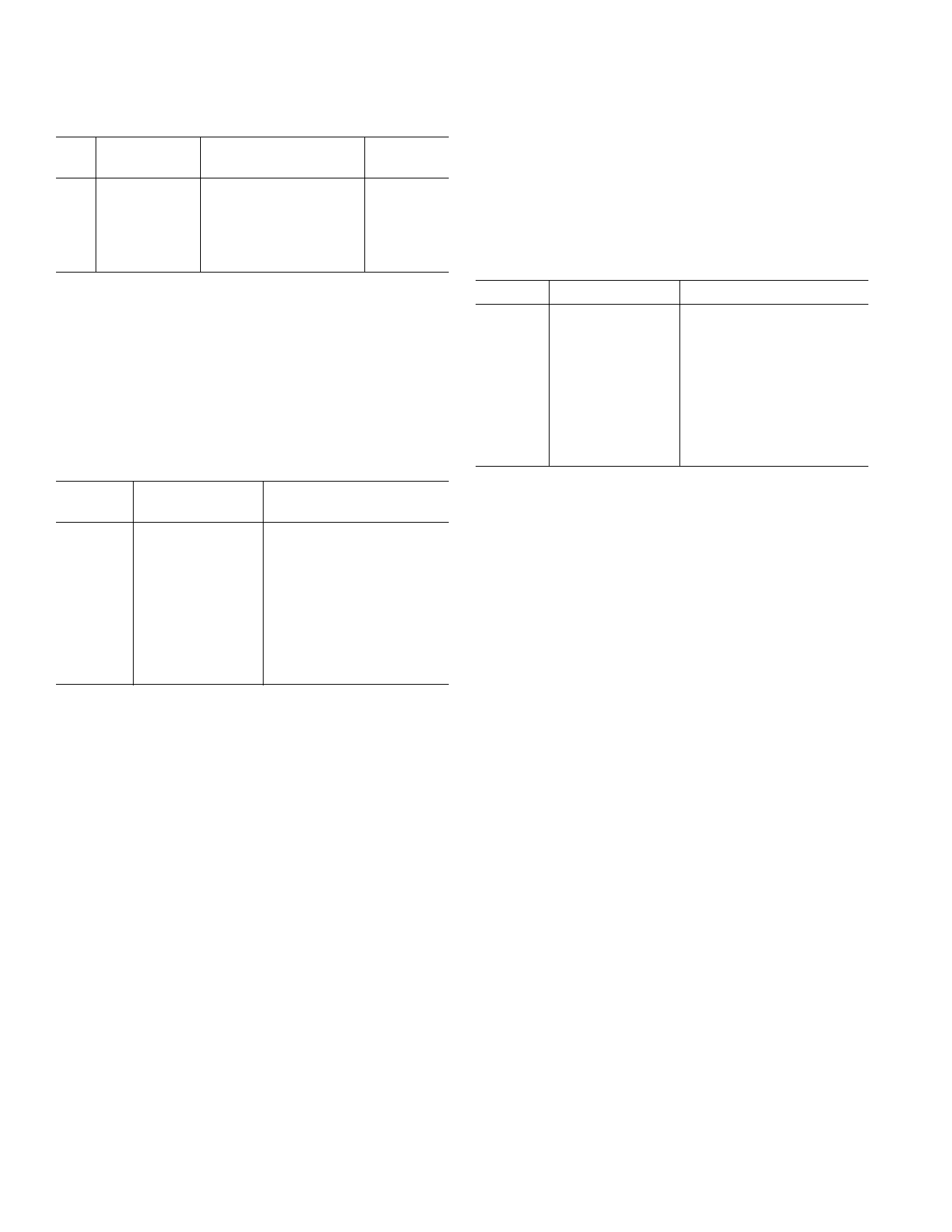

Table IV. Configuration Register Bit Assignments

Bit Name

Function

Power-On

Default

7

MASK1

0 = ALERT Enabled 0

1 = ALERT Masked

6

RUN/STOP 0 = Run

0

1 = Standby

5-0

Reserved

0

Conversion Rate Register

The lowest three bits of this register are used to program the

conversion rate by dividing the ADC clock by 1, 2, 4, 8, 16, 32,

64 or 128, to give conversion times from 125 ms (Code 07h) to

16 seconds (Code 00h). This register can be written to and read

back over the SMBus. The higher five bits of this register are

unused and must be set to zero. Use of slower conversion times

greatly reduces the device power consumption, as shown in

Table V.

Table V. Conversion Rate Register Codes

Data

00h

01h

02h

03h

04h

05h

06h

07h

08h to FFh

Conversion/sec

0.0625

0.125

0.25

0.5

1

2

4

8

Reserved

Average Supply Current

A Typ at VCC = 3.3 V

42

42

42

48

60

82

118

170

Limit Registers

The ADM1021 has four limit registers to store local and re-

mote, high and low temperature limits. These registers can be

written to and read back, over the SMBus. The high limit regis-

ters perform a > comparison while the low limit registers per-

form a < comparison. For example, if the high limit register is

programmed as a limit of 80°C, measuring 81°C will result in

an alarm condition.

One-Shot Register

The one-shot register is used to initiate a single conversion and

comparison cycle when the ADM1021 is in standby mode, after

which the device returns to standby. This is not a data register

as such and it is the write operation that causes the one-shot

conversion. The data written to this address is irrelevant and is

not stored.

SERIAL BUS INTERFACE

Control of the ADM1021 is carried out via the serial bus. The

ADM1021 is connected to this bus as a slave device, under the

control of a master device, e.g., the PIIX4.

ADDRESS PINS

In general, every SMBus device has a 7-bit device address

(except for some devices that have extended, 10-bit addresses).

When the master device sends a device address over the bus, the

slave device with that address will respond. The ADM1021 has

two address pins, ADD0 and ADD1, to allow selection of the

device address, so that several ADM1021s can be used on the

same bus, and/or to avoid conflict with other devices. Although

only two address pins are provided, these are three-state, and

can be grounded, left unconnected, or tied to VDD, so that a

total of nine different addresses are possible, as shown in Table VI.

It should be noted that the state of the address pins is only sampled

at power-up, so changing them after power-up will have no effect.

Table VI. Device Addresses

ADD0

ADD1

Device Address

0

0

0

NC

0

1

NC

0

NC

NC

NC

1

1

0

1

NC

1

1

0011 000

0011 001

0011 010

0101 001

0101 010

0101 011

1001 100

1001 101

1001 110

Note: ADD0, ADD1 sampled at power-up only.

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a START

condition, defined as a high-to-low transition on the serial

data line SDATA, while the serial clock line SCLK remains

high. This indicates that an address/data stream will follow.

All slave peripherals connected to the serial bus respond to

the START condition and shift in the next eight bits, con-

sisting of a 7-bit address (MSB first) plus an R/W bit, which

determines the direction of the data transfer, i.e., whether

data will be written to or read from the slave device.

The peripheral whose address corresponds to the transmitted

address responds by pulling the data line low during the low

period before the ninth clock pulse, known as the Acknowl-

edge Bit. All other devices on the bus now remain idle while

the selected device waits for data to be read from or written

to it. If the R/W bit is a 0, then the master will write to the

slave device. If the R/W bit is a 1, the master will read from

the slave device.

2. Data is sent over the serial bus in sequences of nine clock

pulses, eight bits of data followed by an Acknowledge Bit

from the slave device. Transitions on the data line must

occur during the low period of the clock signal and remain

stable during the high period, as a low-to-high transition

when the clock is high may be interpreted as a STOP signal.

The number of data bytes that can be transmitted over the

serial bus in a single READ or WRITE operation is limited

only by what the master and slave devices can handle.

3. When all data bytes have been read or written, stop condi-

tions are established. In WRITE mode, the master will pull

the data line high during the 10th clock pulse to assert a

STOP condition. In READ mode, the master device will

override the acknowledge bit by pulling the data line high

during the low period before the ninth clock pulse. This is

known as No Acknowledge. The master will then take the

data line low during the low period before the 10th clock

pulse, then high during the 10th clock pulse to assert a STOP

condition.

–8–

REV. 0