CY7C1366A View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

Manufacturer

CY7C1366A Datasheet PDF : 27 Pages

| |||

CY7C1366A/GVT71256C36

CY7C1367A/GVT71512C18

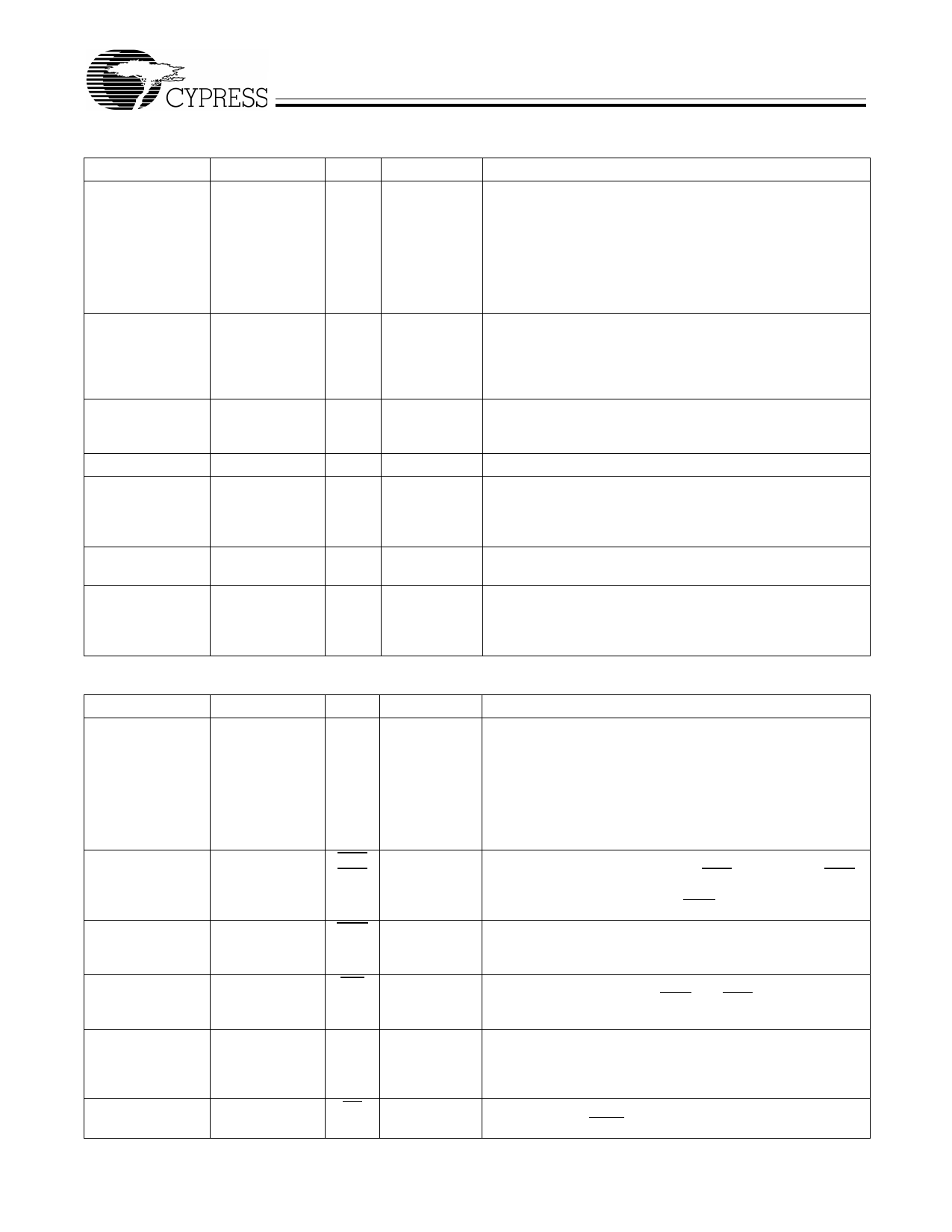

256K X 36 Pin Descriptions (continued)

X36 PBGA Pins X36 QFP Pins Name

(a) 6P, 7P, 7N, 6N, (a) 51, 52, 53, 56,

6M, 6L, 7L, 6K, 7K, 57, 58, 59, 62, 63

(b) 7H, 6H, 7G, 6G, (b) 68, 69, 72, 73,

6F, 6E, 7E, 7D, 6D, 74, 75, 78, 79, 80

(c) 2D, 1D, 1E, 2E, (c) 1, 2, 3, 6, 7, 8,

2F, 1G, 2G, 1H, 2H,

9, 12, 13

(d) 1K, 2K, 1L, 2L, (d) 18, 19, 22, 23,

2M, 1N, 2N, 1P, 2P 24, 25, 28, 29, 30

DQa

DQb

DQc

DQd

2U

38

TMS

3U

39

TDI

4U

43

TCK

for B and T

version

5U

42

TDO

for B and T

version

4C, 2J, 4J, 6J, 4R 15, 41,65, 91 VCC

3D, 5D, 3E, 5E, 3F, 5, 10, 17, 21, 26, VSS

5F, 3H, 5H, 3K, 5K, 40, 55, 60, 67,

3M, 5M, 3N, 5N,

71, 76, 90

3P, 5P

1A, 7A, 1F, 7F, 1J, 4, 11, 20, 27, 54, VCCQ

7J, 1M, 7M, 1U, 7U 61, 70, 77

1B, 7B, 1C, 7C, 4D, 14, 16, 66

NC

3J, 5J, 4L, 1R, 5R,

7R, 1T, 2T, 6T, 6U 38, 39, 42 for TA

Version

Type

Input/

Output

Input

Output

Supply

Ground

I/O Supply

-

Description

Data Inputs/Outputs: First Byte is DQa. Second Byte is DQb.

Third Byte is DQc. Fourth Byte is DQd. Input data must meet

set-up and hold times around the rising edge of CLK.

IEEE 1149.1 test inputs. LVTTL-level inputs. Not available for

TA package version.

IEEE 1149.1 test output. LVTTL-level output. Not available for

TA package version.

Core power Supply: +3.3V –5% and +10%

Ground: GND.

Output Buffer Supply: +2.5V or +3.3V.

No Connect: These signals are not internally connected. User

can leave it floating or connect it to VCC or VSS.

512K X 18 Pin Descriptions

X18 PBGA Pins

4P

4N

2A, 3A, 5A, 6A, 3B,

5B, 6B, 2C, 3C, 5C,

6C, 2R, 6R, 2T, 3T,

5T, 6T

5L

3G

X18 QFP Pins

37

36

35, 34, 33, 32,

100, 99, 82, 81,

80, 48, 47, 46,

45, 44, 49, 50

92 (T Version)

43 (TA Version)

93

94

4M

87

4H

88

4K

89

4E

98

Name

A0

A1

A

BWa

BWb

BWE

GW

CLK

CE

Type

Description

Input-

Synchronous

Addresses: These inputs are registered and must meet the

set-up and hold times around the rising edge of CLK. The burst

counter generates internal addresses associated with A0 and

A1, during burst cycle and wait cycle.

Input-

Synchronous

Byte Write Enables: A byte write enable is LOW for a WRITE

cycle and HIGH for a READ cycle. BWa controls DQa. BWb

controls DQb. Data I/O are high impedance if either of these

inputs are LOW, conditioned by BWE being LOW.

Input-

Write Enable: This active LOW input gates byte write opera-

Synchronous tions and must meet the set up and hold times around the rising

edge of CLK.

Input-

Global Write: This active LOW input allows a full 18-bit WRITE

Synchronous to occur independent of the BWE and WEn lines and must

meet the set up and hold times around the rising edge of CLK.

Input-

Synchronous

Clock: This signal registers the addresses, data, chip enables,

write control and burst control inputs on its rising edge. All

synchronous inputs must meet setup and hold times around

the clock’s rising edge.

Input-

Chip Enable: This active LOW input is used to enable the de-

Synchronous vice and to gate ADSP.

6