GVT71256D36T-4.4 View Datasheet(PDF) - Cypress Semiconductor

Part Name

Description

Manufacturer

GVT71256D36T-4.4 Datasheet PDF : 27 Pages

| |||

PRELIMINARY

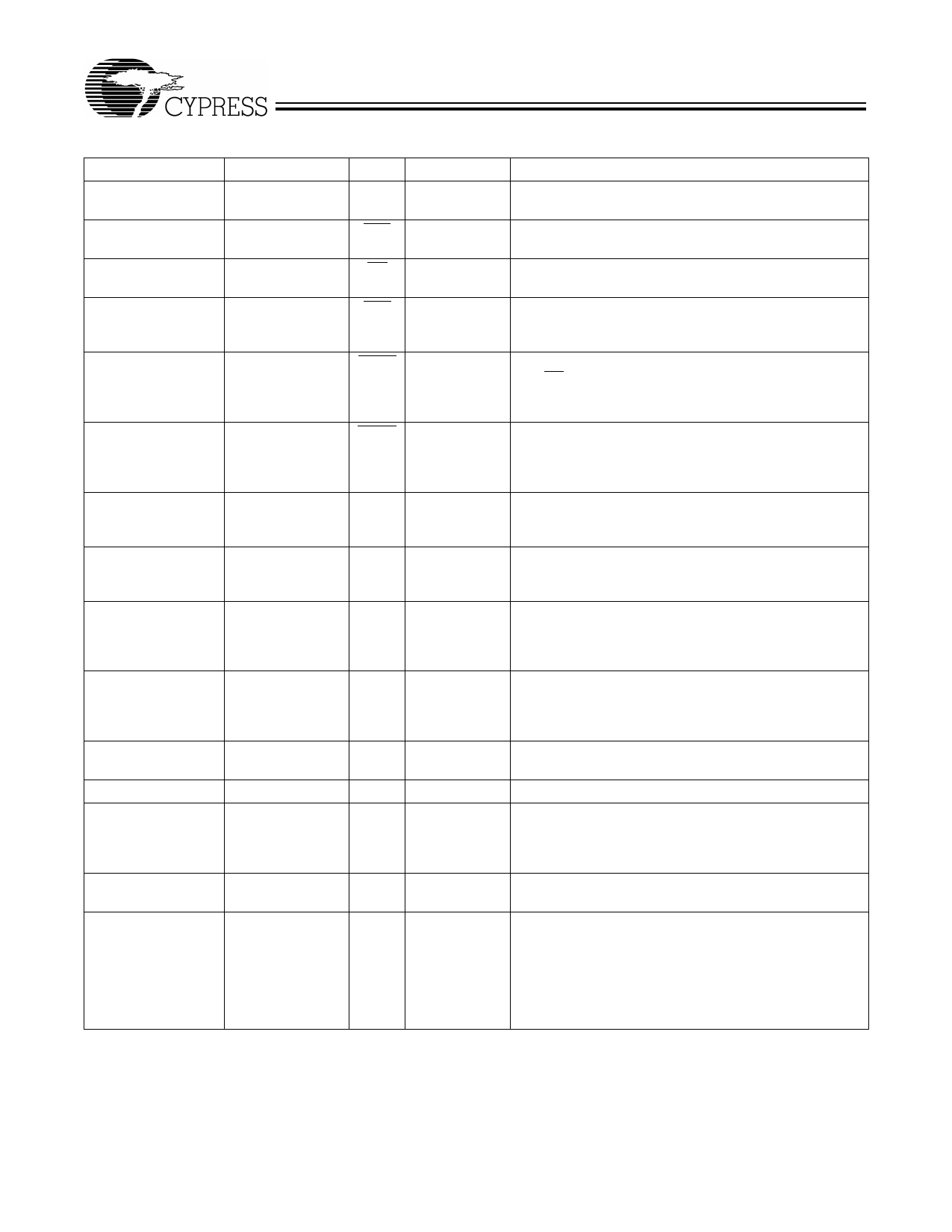

CY7C1360A/GVT71256D36

CY7C1362A/GVT71512D18

512K X 18 Pin Descriptions (continued)

X18 PBGA Pins

2B

- (not available for

PBGA)

4F

4G

4A

4B

3R

7T

(a) 6D, 7E, 6F, 7G,

6H, 7K, 6L, 6N, 7P

(b) 1D, 2E, 2G, 1H,

2K, 1L, 2M, 1N, 2P

2U

3U

4U

5U

4C, 2J, 4J, 6J, 4R

3D, 5D, 3E, 5E, 3F,

5F, 5G, 3H, 5H, 3K,

5K, 3L, 3M, 5M, 3N,

5N, 3P, 5P

1A, 7A, 1F, 7F, 1J, 7J,

1M, 7M, 1U, 7U

1B, 7B, 1C, 7C, 2D,

4D, 7D, 1E, 6E, 2F,

1G, 6G, 2H, 7H, 3J,

5J, 1K, 6K, 2L, 4L,

7L, 6M, 2N, 7N, 1P,

6P, 1R, 5R, 7R, 1T,

4T, 6U

X18 QFP Pins

97

92 (for TA Version

only)

86

83

84

85

31

64

(a) 58, 59, 62, 63,

68, 69, 72, 73, 74

(b) 8, 9, 12, 13, 18,

19, 22, 23, 24

38

39

43

for B and T version

42

for B and T version

15, 41,65, 91

5, 10, 17, 21, 26,

40, 55, 60, 67, 71,

76, 90

4, 11, 20, 27, 54,

61, 70, 77

1–3, 6, 7, 14, 16,

25, 28–30, 51–53,

56, 57, 66, 75, 78,

79, 80, 95, 96

38, 39, 42 for TA

Version

Name

CE2

CE2

OE

ADV

ADSP

ADSC

MODE

ZZ

DQa

DQb

TMS

TDI

TCK

TDO

VCC

VSS

VCCQ

NC

Type

Input-

Synchronous

Input-

Synchronous

Input

Input-

Synchronous

Input-

Synchronous

Input-

Synchronous

Input-

Static

Input-

Asynchronous

Input/

Output

Input

Output

Supply

Ground

I/O Supply

-

Description

Chip Enable: This active HIGH input is used to enable the

device.

Chip Enable: This active LOW input is used to enable the

device. Not available for B and T package versions.

Output Enable: This active LOW asynchronous input en-

ables the data output drivers.

Address Advance: This active LOW input is used to con-

trol the internal burst counter. A HIGH on this pin gener-

ates wait cycle (no address advance).

Address Status Processor: This active LOW input, along

with CE being LOW, causes a new external address to be

registered and a READ cycle is initiated using the new

address.

Address Status Controller: This active LOW input causes

device to be deselected or selected along with new exter-

nal address to be registered. A READ or WRITE cycle is

initiated depending upon write control inputs.

Mode: This input selects the burst sequence. A LOW on

this pin selects Linear Burst. An NC or HIGH on this pin

selects Interleaved Burst.

Snooze: This active HIGH input puts the device in low

power consumption standby mode. For normal operation,

this input has to be either LOW or NC (No Connect).

Data Inputs/Outputs: Low Byte is DQa. High Byte is DQb.

Input data must meet set up and hold times around the

rising edge of CLK.

IEEE 1149.1 test inputs. LVTTL-level inputs. Not available

for TA package version.

IEEE 1149.1 test output. LVTTL-level output. Not avail-

able for TA package version.

Core power Supply: +3.3V –5% and +10%

Ground: GND.

Output Buffer Supply: +2.5V or +3.3V.

No Connect: These signals are not internally connected.

User can leave it floating or connect it to VCC or VSS.

7