MPC2104 View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MPC2104

MPC2104 Datasheet PDF : 24 Pages

| |||

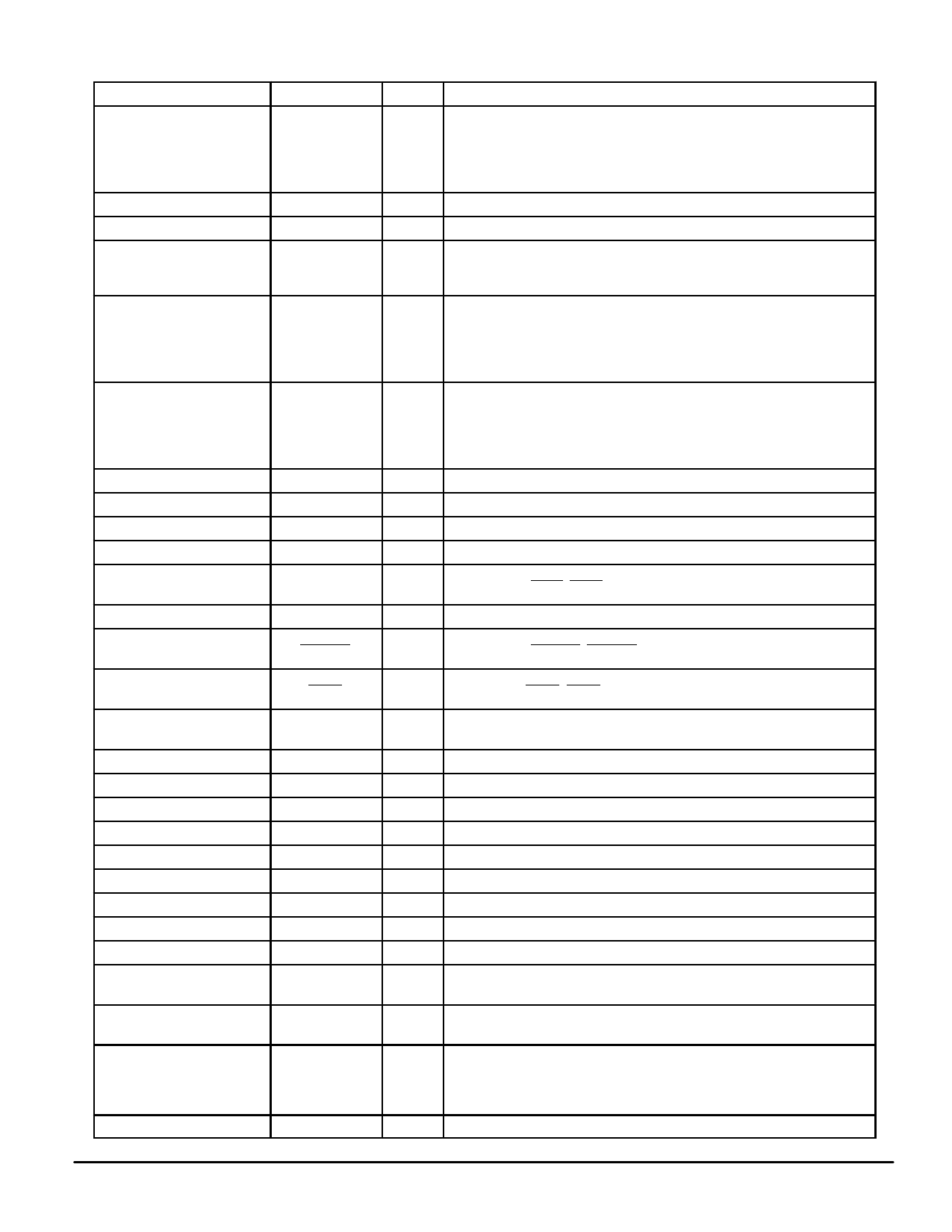

PIN DESCRIPTIONS

Pin Locations

68, 69, 70, 71, 73, 74, 75, 76,

78, 79, 80, 82, 83, 84, 85,

159, 160, 161, 162, 164, 165,

166, 167, 169, 170, 171, 173,

174, 175

62

153

30, 56, 117, 146, 148

Symbol

A0 – A28

ADDR0

ADDR1

CLK0 – CLK4

4, 5, 6, 7, 10, 11, 12, 14, 16,

17, 19, 20, 22, 24, 25, 26, 27,

95, 96, 97, 98, 101, 102, 103,

105, 107, 108, 110, 111, 113,

115, 119

32, 33, 34, 37, 38, 39, 40, 43,

44, 45, 47, 49, 50, 52, 53, 54,

121, 122, 124, 125, 126, 129,

130, 131, 133, 135, 136, 138,

139, 141, 143, 144

9, 15, 21, 28, 35, 42, 48, 58

3, 94

2

93

64, 65

DH0 – DH31

DL0 – DL31

DP0 – DP7

PD2, PD3

PD0/IDSCLK

PD1/IDSDATA

ADS0, ADS1

151

155, 156

59, 60

100, 106, 112, 120,

128, 134, 140, 150

87

88

178

179

89

90

181

180

176, 63, 154

8, 23, 51, 61, 77, 99, 114,

142, 152, 168

18, 36, 66, 67, 86, 109, 127,

157, 158, 177

1, 13, 29, 31, 41, 46, 55, 57,

72, 81, 91, 92, 104, 116,

118, 123, 132, 137, 145,

147, 149, 163, 172, 182

176

ALE

CNTEN0,

CNTEN1

COE0,

COE1

CWE0 – CWE7

TCLR

MATCH

VALIDIN

TWE

TOE

DIRTYIN

DIRTYOUT

STANDBY

RESERVED

VCC3

VCC5

VSS

BURSTMODE

Type

Input

Description

Address Inputs – (MSB:0, LSB:28)

Input

Input

Input

I/O

Least significant address bit when asynchronous Data RAMs are used.

Next to least significant address bit when asynchronous Data RAMs are used.

Clock Inputs – CLK2 is for Tag RAM, CLK0, 1, 3, and 4 are for Data RAMs only.

For MPC2106 use all the clocks. For MPC2104 or MPC2105 use CLK0–CLK2

only. For MPC2107 use CLK2 only.

High Data Bus – (MSB:0, LSB:31)

I/O Low Data Bus – (MSB:0, LSB:31)

I/O Data Parity Bits – (MSB:0, LSB:7)

Output Presence detect bits.

Input Presence detect bit 0/EEPROM serial clock. (EEPROM option only.)

I/O Presence detect bit 1/EEPROM serial data. (EEPROM option only.)

Input Data RAM Address Strobe – For MPC2104 or MPC2105 use ADS0 only. For

MPC2106 use ADS0, ADS1.

Input Data RAM Address Latch Enable – Use for asynchronous Data RAM only.

Input Data RAM Count Enables – For MPC2104 or MPC2105 use CNTEN0 only. For

MPC2106 use CNTEN0, CNTEN1.

Input Data RAM Output Enables – For MPC2104 or MPC2105 use COE0 only. For

all others use COE0, COE1.

Input Data RAM Write Enables – (MSB:0, LSB:7)

Input

Output

Input

Input

Input

Input

Output

Input

Input

Tag RAM clear.

Tag RAM active high match indication.

Tag RAM valid bit.

Tag RAM write enable.

Tag RAM output enable.

Dirty input bit.

Dirty output bit.

Standby pin. Reduces standby power consumption.

Reserved pin.

+ 3.3 V power supply. Must be connected.

Input + 5 V power supply. Must be connected.

Input Ground

Input Burstmode. 0 = Linear, 1 = Interleaved.

MPC2104•MPC2105•MPC2106•MPC2107

6

MOTOROLA FAST SRAM