CDB5366 View Datasheet(PDF) - Cirrus Logic

Part Name

Description

Manufacturer

CDB5366 Datasheet PDF : 42 Pages

| |||

CS5366

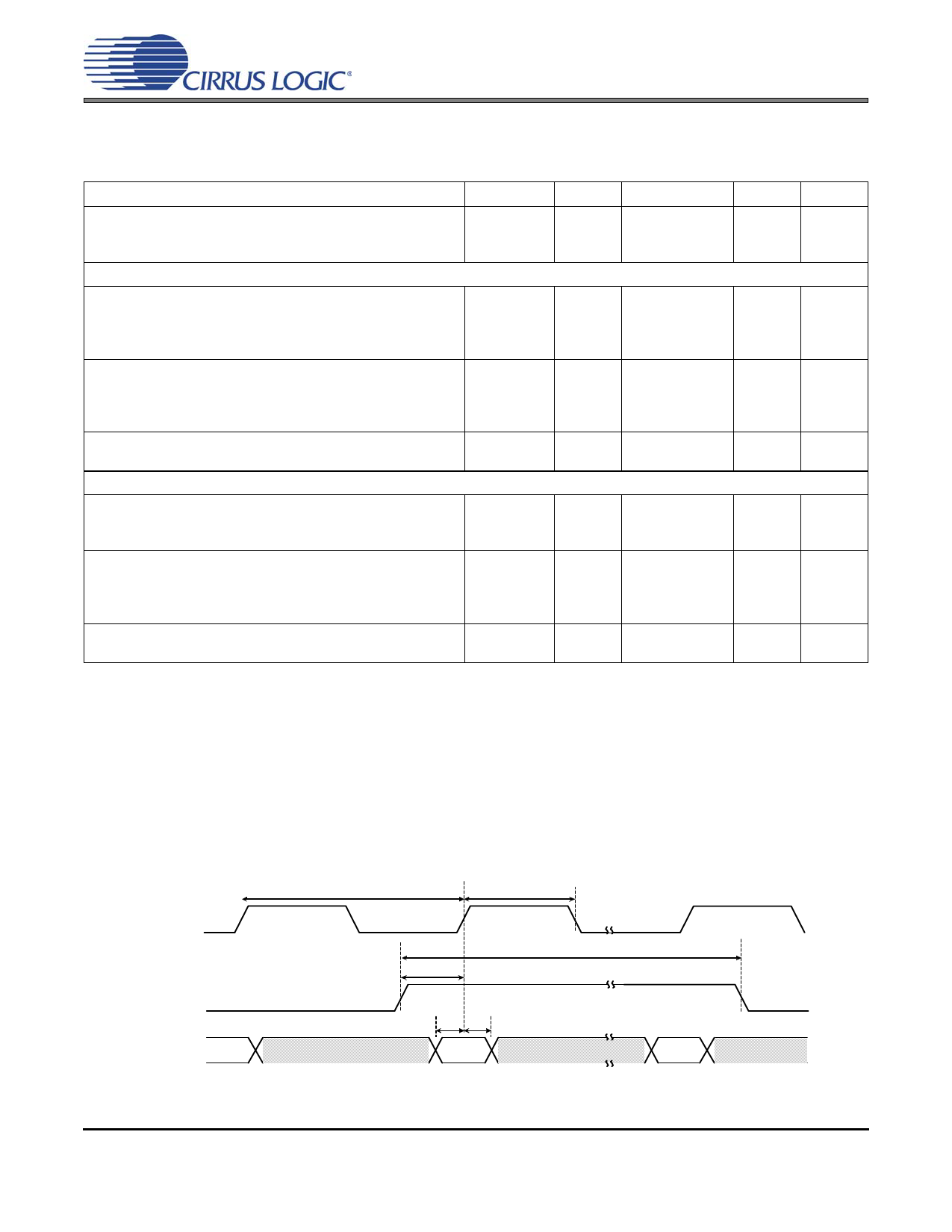

SERIAL AUDIO INTERFACE - TDM TIMING

The serial audio port is a three-pin interface consisting of SCLK, LRCK and SDOUT.

Logic "0" = GND = 0 V; Logic "1" = VLS; CL = 20 pF, timing threshold is 50% of VLS.

Parameter

Symbol Min

Typ

Sample Rates

Single-Speed Mode

-

2

-

Double-Speed Mode

-

54

-

Quad-Speed Mode1

-

108

-

Master Mode

SCLK Frequency

256*Fs

-

SCLK Period

1/(256*216 kHz) tPERIOD

18

-

SCLK Duty Cycle (Note 2)

(CLKMODE = 0)(Note 3) tHIGH1

40

50

(CLKMODE = 1)(Note 3) tHIGH1

28

33

FS setup

before SCLK rising (Single-Speed Mode) tSETUP1

20

-

FS setup

before SCLK rising (Double-Speed Mode) tSETUP1

18

-

FS setup

before SCLK rising (Quad-Speed Mode) tSETUP1

5

-

FS width

in SCLK cycles tHIGH2

128

-

SDOUT setup

SDOUT hold

before SCLK rising tSETUP2

5

-

after SCLK rising tHOLD2

5

-

Slave Mode

SCLK Frequency (Note 4)

-

SCLK Period

SCLK Duty Cycle

1/(256*216 kHz) tPERIOD

18

tHIGH1

28

FS setup

FS setup

FS setup

FS width

before SCLK rising (Single-Speed Mode) tSETUP1

20

before SCLK rising (Double-Speed Mode) tSETUP1

20

before SCLK rising (Quad-Speed Mode) tSETUP1

10

in SCLK cycles tHIGH2

1

SDOUT setup

SDOUT hold

before SCLK rising tSETUP2

5

after SCLK rising tHOLD2

5

256*Fs

-

-

-

-

-

-

-

-

Max

54

108

216

Unit

kHz

kHz

kHz

256*Fs

Hz

-

ns

60

%

38

%

-

ns

-

ns

-

ns

128

-

-

ns

-

ns

-

Hz

-

ns

65

%

-

ns

-

ns

-

ns

244

-

-

ns

-

ns

Notes:

1. TDM Quad-Speed Mode only specified to operate correctly at VLS ≥ 3.14 V.

2. Duty cycle of generated SCLK depends on duty cycle of received MCLK as specified under “System

Clocking” on page 10.

3. CLKMODE functionality described in Section 4.6.3 "Master Mode Clock Dividers" on page 24.

4. In Slave Mode, the SCLK/LRCK ratio can be set according to preference; chip performance is guaran-

teed only when using the ratios in Section 4.7 Master and Slave Clock Frequencies on page 25.

t PERIOD

t HIGH1

SCLK

FS

SDOUT

data

t SETUP1

t HIGH2

new frame

t SETUP2

data

t HOLD2

Figure 4. TDM Timing

data

16

DS626F4