DSP56166 View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

DSP56166 Datasheet PDF : 63 Pages

| |||

INTRODUCTION

This data sheet is intended to be used with the DSP56100 Fam-

ily Manual and the DSP56166 User’s Manual. The DSP56100

Family Manual provides a description of the components of the

DSP5616 core processor that are common to all DSP56100 fam-

ily processors and includes a detailed description of the basic

DSP56100 family instruction set. The DSP56166 User’s Manual

provides a description of the memory and peripherals that are

specific to the DSP56166. The DSP56166 Data Sheet provides

electrical specifications and timings that are specific to the

DSP56166.

The DSP56166 pinout is shown in Figure 3. The input and output

signals on the chip are organized into the 13 functional groups

shown in Table 1.

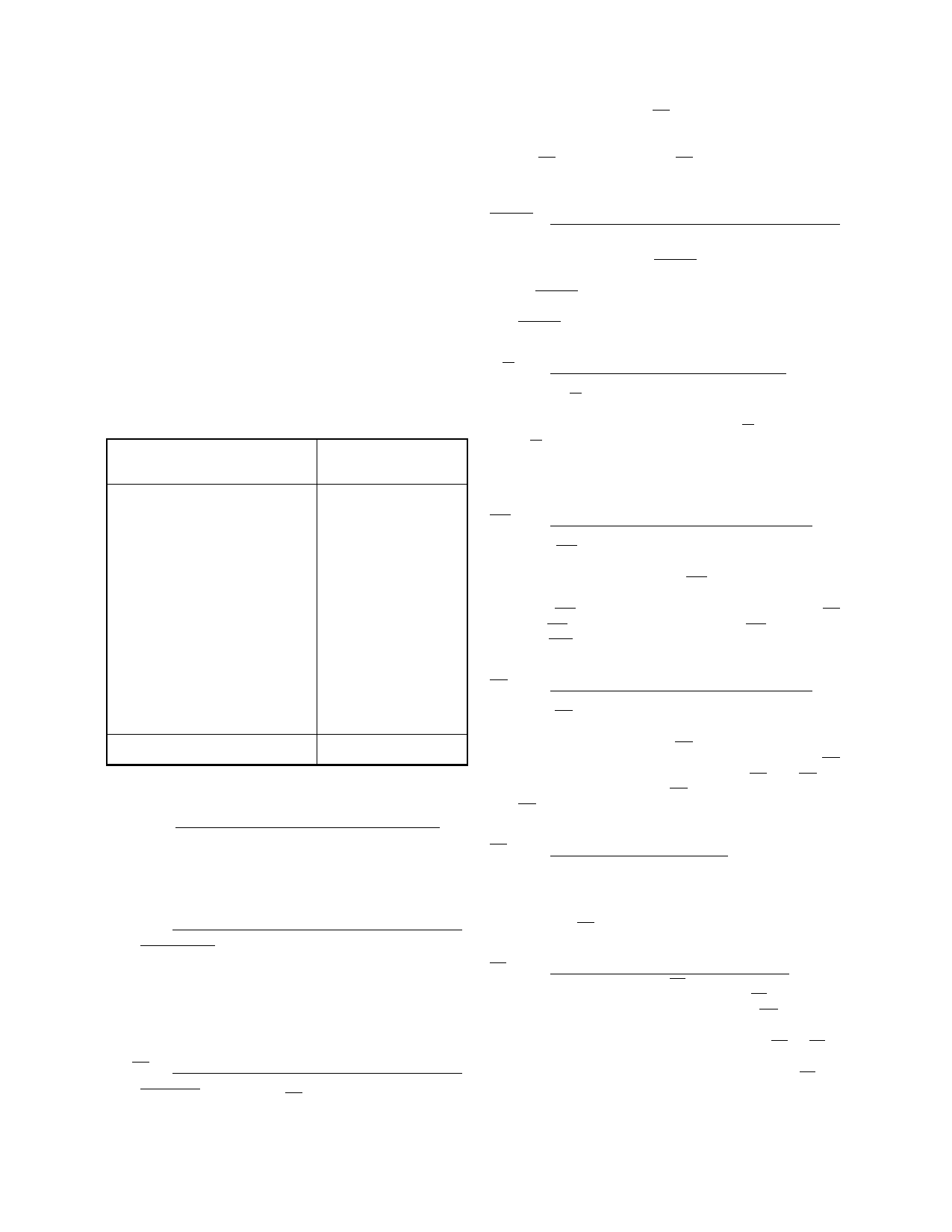

Table 1

Functional Group Pin Allocations

Functional Group

Number of Pins

Address and Data Buses

32

Bus Control

10

Interrupt and Mode Control

4

Clock and PLL

3

Host Interface or PIO

15

Timer Interface or PIO

2

RSSI Interfaces or PIO

8

On-chip CODEC

7

On-chip emulation (OnCE)

4

Power (Vdd)

9

Ground (Vss)

16

APower (Vdda)

1

AGround (Vssa)

1

Total

112

ADDRESS AND DATA BUS (32 PINS

A0-A15 (Address Bus) — three state, active high outputs. A0-

A15 change in t0 and specify the address for external

program and data memory accesses. If there is no external

bus activity, A0-A15 remain at their previous values. A0-

A15 are three-stated during hardware reset, stop mode and

when the DSP is not the bus master.

D0-D15 (Data Bus) — three state, active high, bidirectional

input/outputs. Read data is sampled on the trailing edge of

t2, while write data output is enabled by the leading edge of

t2 and three-stated at the leading edge of t0. If there is no

external bus activity, D0-D15 are three-stated. D0-D15 are

also three-stated during hardware reset.

BUS CONTROL (10 PINS)

PS/DS (Program /Data Memory Select) — three state active

low output. This output is asserted only when external data

memory is referenced. PS/DS timing is the same for the A0-

A15 address lines. PS/DS is high for program memory

access and is low for data memory access. If the external

bus is not used during an instruction cycle (t0,t1,t2,t3),

PS/DS goes high in t0. PS/DS is in the high impedance

state during hardware reset, stop mode and when the DSP

is not the bus master.

PEREN (Peripheral Enable) — three state active low output.

This output is asserted only when external peripheral space

of the data memory is referenced (any address between

X:$FF00 and X:$FF7F). PEREN timing is the same as the

A0-A15 address lines; it is asserted and deasserted during

t0. PEREN is high for any program memory access and for

data memory access not in the space X:$FF00 - X:$FF7F.

PEREN is in the high impedance state during hardware

reset, stop mode and when the DSP is not the bus master.

R/W (Read/Write)- three state, active low output. Timing is

the same as for the address lines, providing an “early write”

signal. R/W (which changes in t0) is high for a read access

and is low for a write access. If the external bus is not used

during an instruction cycle (t0,t1,t2,t3), R/W goes high in t0.

R/W is three-stated during hardware reset, stop mode and

when the DSP is not the bus master.

WR

(Write Enable) — three state, active low output. This

output is asserted during external memory write cycles.

When WR is asserted in t1, the data bus pins D0-D15

become outputs and the DSP puts data on the bus during

the leading edge of t2. When WR is deasserted in t3, the

external data has been latched inside the external device.

When WR is asserted, it qualifies the A0-A15 and PS/DS

pins. WR can be connected directly to the WE pin of a static

RAM. WR is three-stated during hardware reset, stop mode

and when the DSP is not the bus master.

RD

(Read Enable) — three state, active low output. This

output is asserted during external memory read cycles.

When RD is asserted in late t0/early t1, the data bus pins

D0-D15 become inputs and an external device is enabled

onto the data bus. When RD is deasserted in t3, the

external data has been latched inside the DSP. When RD

is asserted, it qualifies the A0-A15 and PS/DS pins. RD can

be connected directly to the OE pin of a static RAM or ROM.

RD is three-stated during hardware reset, stop mode and

when the DSP is not the bus master.

BS

(Bus Strobe) — active low output. Asserted at the start

of a bus cycle (during t0) and deasserted at the end of the

bus cycle (during t2). This pin provides an “early bus start”

signal which can be used as address latch and as an “early

bus end” signal which can be used by an external bus

controller. BS is three-stated during hardware reset, stop

mode and when the DSP is not the bus master.

TA

(Transfer Acknowledge) — active low input. If there is

no external bus activity, the TA input is ignored by the DSP.

When there is external bus cycle activity, TA can be used

to insert wait states in the external bus cycle. TA is sampled

on the leading edge of the clock. Any number of wait states

from 1 to infinity may be inserted by using TA. If TA is

sampled high on the leading edge of the clock beginning

the bus cycle, the bus cycle will end 2T after the TA has

been sampled low on a leading edge of the clock; if the Bus

Control Register (BCR) value does not program more wait

DSP56166

PRELIMINARY

MOTOROLA

3