DSP56300 View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

DSP56300 Datasheet PDF : 108 Pages

| |||

Enhanced Synchronous Serial Interface 0 (ESSI0)

1.8 Enhanced Synchronous Serial Interface 0 (ESSI0)

Two synchronous serial interfaces (ESSI0 and ESSI1) provide a full-duplex serial port for serial communication

with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors, and

peripherals that implement the serial peripheral interface (SPI).

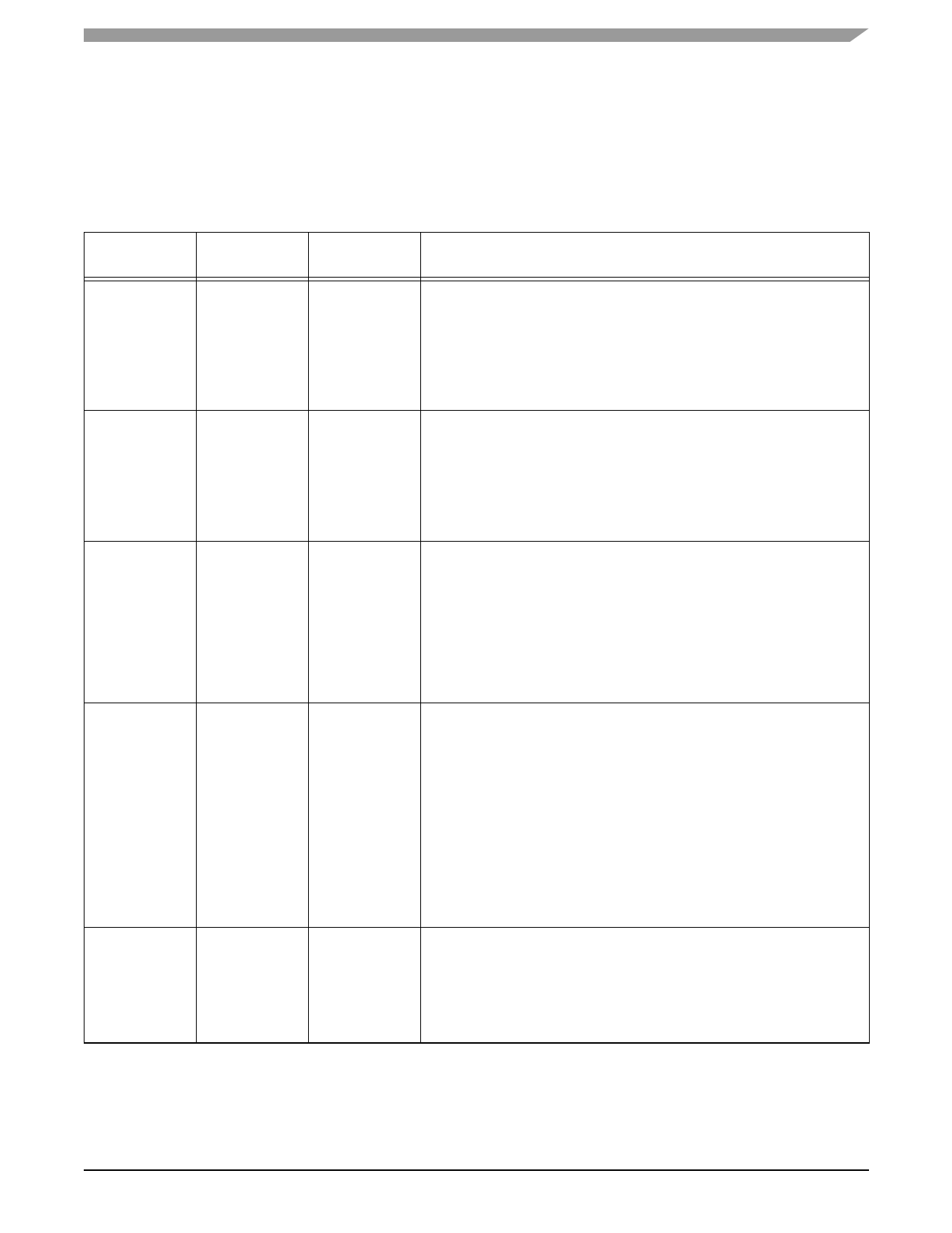

Table 1-12. Enhanced Synchronous Serial Interface 0

Signal Name

Type

SC00

Input or Output

State During

Reset1,2

Ignored Input

Signal Description

Serial Control 0—For asynchronous mode, this signal is used for the receive

clock I/O (Schmitt-trigger input). For synchronous mode, this signal is used

either for transmitter 1 output or for serial I/O flag 0.

PC0

SC01

Input or Output

Input/Output

Ignored Input

Port C 0—The default configuration following reset is GPIO input PC0. When

configured as PC0, signal direction is controlled through the Port C Direction

Register. The signal can be configured as ESSI signal SC00 through the Port C

Control Register.

Serial Control 1—For asynchronous mode, this signal is the receiver frame

sync I/O. For synchronous mode, this signal is used either for transmitter 2

output or for serial I/O flag 1.

PC1

SC02

Input or Output

Input/Output

Ignored Input

Port C 1—The default configuration following reset is GPIO input PC1. When

configured as PC1, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SC01 through the Port

C Control Register.

Serial Control Signal 2—The frame sync for both the transmitter and receiver

in synchronous mode, and for the transmitter only in asynchronous mode. When

configured as an output, this signal is the internally generated frame sync signal.

When configured as an input, this signal receives an external frame sync signal

for the transmitter (and the receiver in synchronous operation).

PC2

SCK0

Input or Output

Input/Output

Ignored Input

Port C 2—The default configuration following reset is GPIO input PC2. When

configured as PC2, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SC02 through the Port

C Control Register.

Serial Clock—Provides the serial bit rate clock for the ESSI. The SCK0 is a

clock input or output, used by both the transmitter and receiver in synchronous

modes or by the transmitter in asynchronous modes.

Although an external serial clock can be independent of and asynchronous to

the DSP system clock, it must exceed the minimum clock cycle time of 6T (that

is, the system clock frequency must be at least three times the external ESSI

clock frequency). The ESSI needs at least three DSP phases inside each half of

the serial clock.

PC3

SRD0

Input or Output

Input

Ignored Input

Port C 3—The default configuration following reset is GPIO input PC3. When

configured as PC3, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SCK0 through the Port

C Control Register.

Serial Receive Data—Receives serial data and transfers the data to the ESSI

Receive Shift Register. SRD0 is an input when data is received.

PC4

Input or Output

Port C 4—The default configuration following reset is GPIO input PC4. When

configured as PC4, signal direction is controlled through the Port C Direction

Register. The signal can be configured as an ESSI signal SRD0 through the

Port C Control Register.

Freescale Semiconductor

DSP56309 Technical Data, Rev. 7

1-11