DSP56321 View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

DSP56321 Datasheet PDF : 84 Pages

| |||

Feature

Internal Memories

External Memory

Expansion

Power Dissipation

Packaging

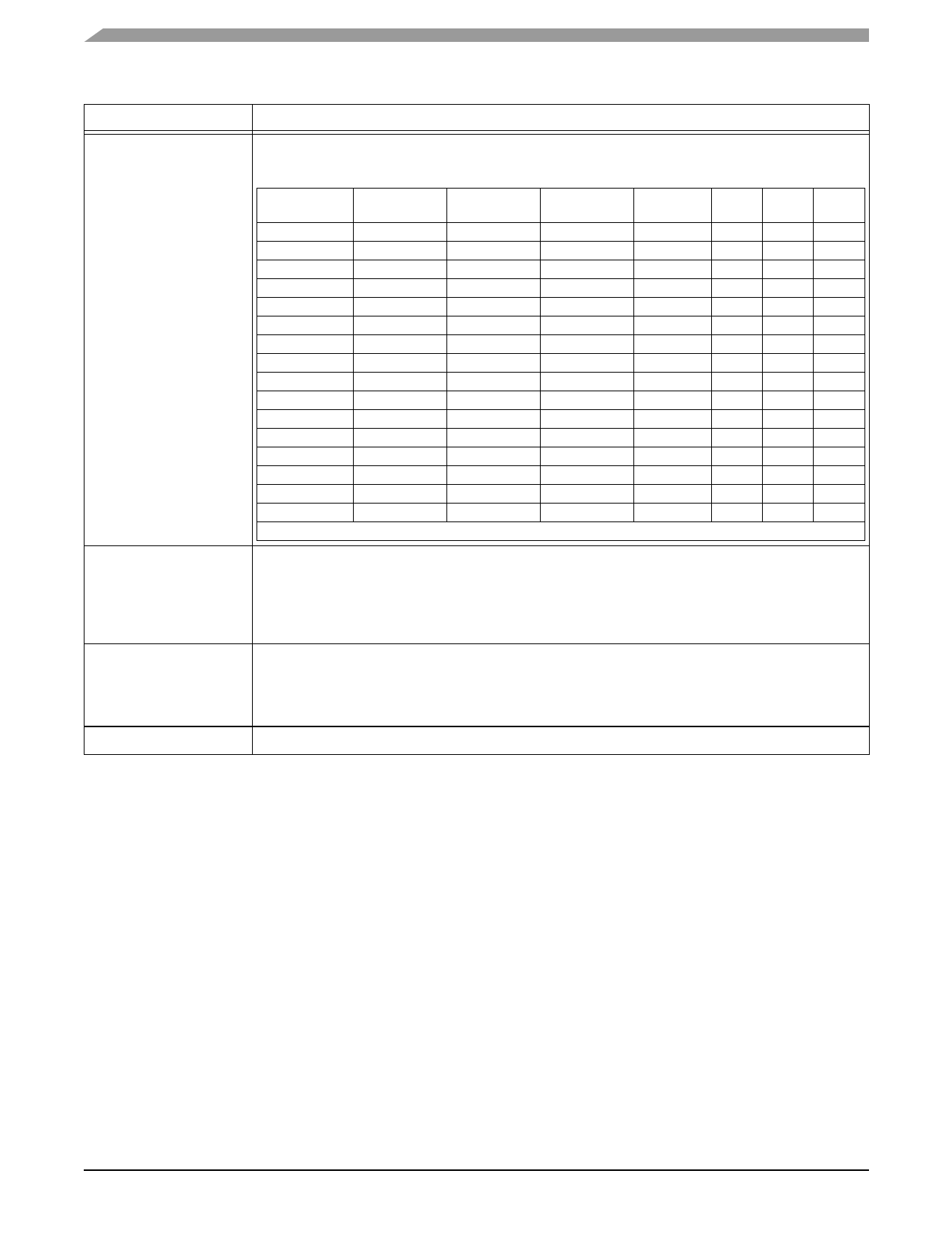

Table 1. DSP56321 Features (Continued)

Description

• 192 × 24-bit bootstrap ROM

• 192 K × 24-bit RAM total

:• Program RAM, instruction cache, X data RAM, and Y data RAM sizes are programmable:

Program RAM Instruction X Data RAM Y Data RAM Instruction MSW2 MSW1

MSW0

Size

Cache Size

Size*

Size*

Cache

32 K × 24-bit

0

80 K × 24-bit 80 K × 24-bit disabled

0

0

0

31 K × 24-bit 1024 × 24-bit 80 K × 24-bit 80 K × 24-bit enabled

0

0

0

40 K × 24-bit

0

76 K × 24-bit 76 K × 24-bit disabled

0

0

1

39 K × 24-bit 1024 × 24-bit 76 K × 24-bit 76 K × 24-bit enabled

0

0

1

48 K × 24-bit

0

72 K × 24-bit 72 K × 24-bit disabled

0

1

0

47 K × 24-bit 1024 × 24-bit 72 K × 24-bit 72 K × 24-bit enabled

0

1

0

64 K × 24-bit

0

64 K × 24-bit 64 K × 24-bit disabled

0

1

1

63 K × 24-bit 1024 × 24-bit 64 K × 24-bit 64 K × 24-bit enabled

0

1

1

72 K × 24-bit

0

60 K × 24-bit 60 K × 24-bit disabled

1

0

0

71 K × 24-bit 1024 × 24-bit 60 K × 24-bit 60 K × 24-bit enabled

1

0

0

80 K × 24-bit

0

56 K × 24-bit 56 K × 24-bit disabled

1

0

1

79 K × 24-bit 1024 × 24-bit 56 K × 24-bit 56 K × 24-bit enabled

1

0

1

96 K × 24-bit

0

48 K × 24-bit 48 K × 24-bit disabled

1

1

0

95 K × 24-bit 1024 × 24-bit 48 K × 24-bit 48 K × 24-bit enabled

1

1

0

112 K × 24-bit

0

40 K × 24-bit 40 K × 24-bit disabled

1

1

1

111 K × 24-bit 1024 × 24-bit 40 K × 24-bit 40 K × 24-bit enabled

1

1

1

*Includes 12 K × 24-bit shared memory (that is, 24 K total memory shared by the core and the EFCOP)

• Data memory expansion to two 256 K × 24-bit word memory spaces using the standard external address

lines

• Program memory expansion to one 256 K × 24-bit words memory space using the standard external

address lines

• External memory expansion port

• Chip select logic for glueless interface to static random access memory (SRAMs)

• Very low-power CMOS design

• Wait and Stop low-power standby modes

• Fully static design specified to operate down to 0 Hz (dc)

• Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-

dependent)

• Molded array plastic-ball grid array (MAP-BGA) package in lead-free or lead-bearing versions.

Target Applications

DSP56321 applications require high performance, low power, small packaging, and a large amount of internal

memory. The EFCOP can accelerate general filtering applications. Examples include:

• Wireless and wireline infrastructure applications

• Multi-channel wireless local loop systems

• Security encryption systems

• Home entertainment systems

• DSP resource boards

• High-speed modem banks

• IP telephony

DSP56321 Technical Data, Rev. 11

iv

Freescale Semiconductor