DSP56366 View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

DSP56366 Datasheet PDF : 110 Pages

| |||

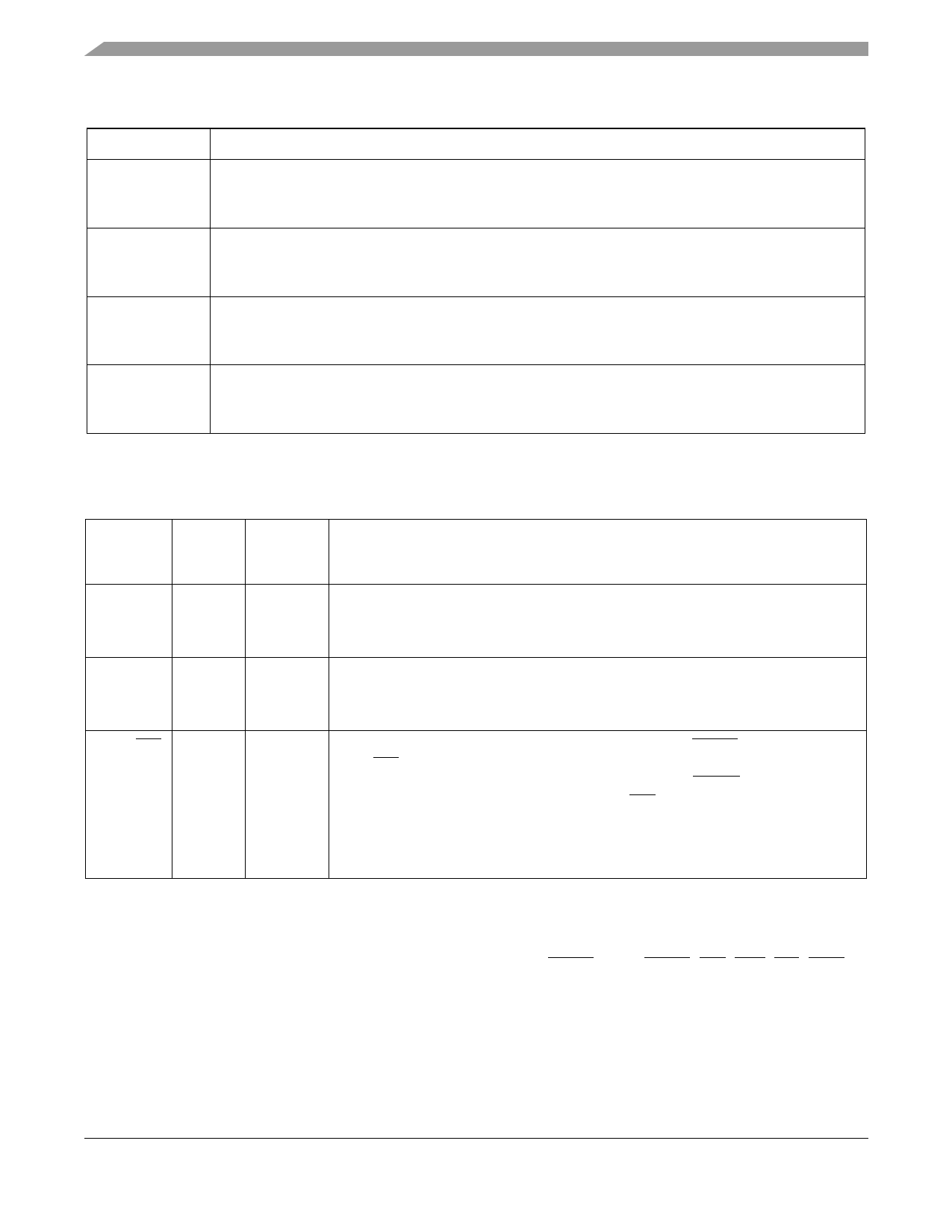

Table 2-3 Grounds (continued)

Ground Name

Description

GNDD (4)

GNDC (2)

GNDH

GNDS (2)

Data Bus Ground—GNDD is an isolated ground for sections of the data bus I/O drivers. This connection

must be tied externally to all other chip ground connections. The user must provide adequate external

decoupling capacitors. There are four GNDD connections.

Bus Control Ground—GNDC is an isolated ground for the bus control I/O drivers. This connection must

be tied externally to all other chip ground connections. The user must provide adequate external

decoupling capacitors. There are two GNDC connections.

Host Ground—GNDh is an isolated ground for the HD08 I/O drivers. This connection must be tied

externally to all other chip ground connections. The user must provide adequate external decoupling

capacitors. There is one GNDH connection.

SHI, ESAI, ESAI_1, DAX and Timer Ground—GNDS is an isolated ground for the SHI, ESAI, ESAI_1,

DAX and Timer. This connection must be tied externally to all other chip ground connections. The user

must provide adequate external decoupling capacitors. There are two GNDS connections.

2.4 Clock and PLL

Table 2-4 Clock and PLL Signals

Signal

Name

EXTAL

Type

Input

PCAP

Input

PINIT/NMI Input

State

during

Reset

Input

Input

Input

Signal Description

External Clock Input—An external clock source must be connected to EXTAL in order

to supply the clock to the internal clock generator and PLL.

This input cannot tolerate 5 V.

PLL Capacitor—PCAP is an input connecting an off-chip capacitor to the PLL filter.

Connect one capacitor terminal to PCAP and the other terminal to VCCP.

If the PLL is not used, PCAP may be tied to VCC, GND, or left floating.

PLL Initial/Nonmaskable Interrupt—During assertion of RESET, the value of

PINIT/NMI is written into the PLL Enable (PEN) bit of the PLL control register,

determining whether the PLL is enabled or disabled. After RESET de assertion and

during normal instruction processing, the PINIT/NMI Schmitt-trigger input is a

negative-edge-triggered nonmaskable interrupt (NMI) request internally synchronized

to internal system clock.

This input cannot tolerate 5 V.

2.5 External Memory Expansion Port (Port A)

When the DSP56366 enters a low-power standby mode (stop or wait), it releases bus mastership and

tri-states the relevant port A signals: A0–A17, D0–D23, AA0/RAS0–AA2/RAS2, RD, WR, BB, CAS.

DSP56366 Technical Data, Rev. 3.1

2-4

Freescale Semiconductor