DSP56367P View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

DSP56367P Datasheet PDF : 100 Pages

| |||

Serial Host Interface

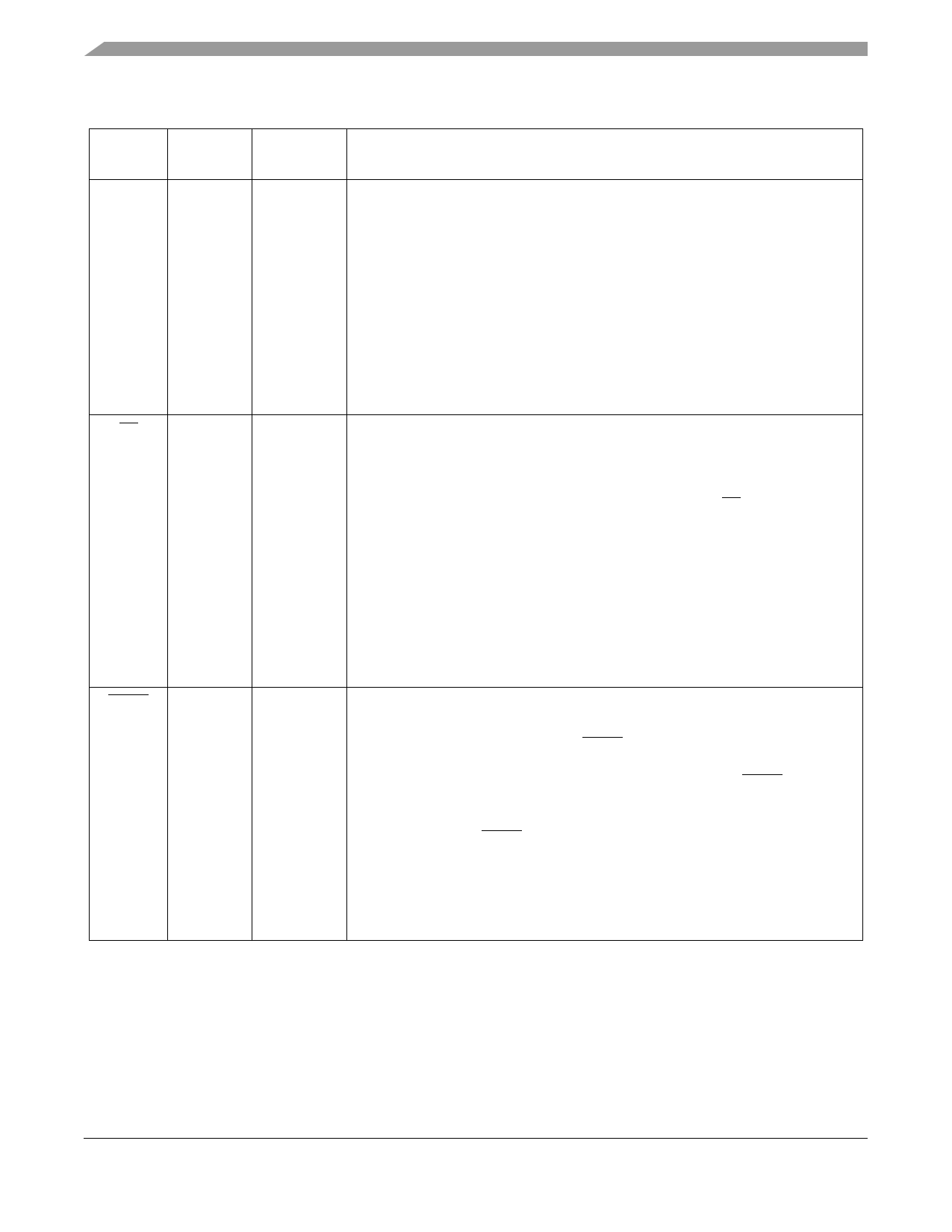

Table 2-10 Serial Host Interface Signals (continued)

Signal

Name

Signal State During

Type

Reset

Signal Description

MOSI

HA0

Input or

Output

Input

Tri-Stated

SPI Master-Out-Slave-In—When the SPI is configured as a master, MOSI is the

master data output line. The MOSI signal is used in conjunction with the MISO

signal for transmitting and receiving serial data. MOSI is the slave data input line

when the SPI is configured as a slave. This signal is a Schmitt-trigger input when

configured for the SPI Slave mode.

I2C Slave Address 0—This signal uses a Schmitt-trigger input when configured for

the I2C mode. When configured for I2C slave mode, the HA0 signal is used to form

the slave device address. HA0 is ignored when configured for the I2C master mode.

This signal is tri-stated during hardware, software, and individual reset. Thus, there

is no need for an external pull-up in this state.

This input is 3.3V tolerant.

SS

Input

Tri-Stated SPI Slave Select—This signal is an active low Schmitt-trigger input when

configured for the SPI mode. When configured for the SPI Slave mode, this signal

is used to enable the SPI slave for transfer. When configured for the SPI master

mode, this signal should be kept deasserted (pulled high). If it is asserted while

configured as SPI master, a bus error condition is flagged. If SS is deasserted, the

SHI ignores SCK clocks and keeps the MISO output signal in the high-impedance

state.

HA2

Input

I2C Slave Address 2—This signal uses a Schmitt-trigger input when configured for

the I2C mode. When configured for the I2C Slave mode, the HA2 signal is used to

form the slave device address. HA2 is ignored in the I2C master mode.

This signal is tri-stated during hardware, software, and individual reset. Thus, there

is no need for an external pull-up in this state.

This input is 3.3V tolerant.

HREQ

Input or

Output

Tri-Stated

Host Request—This signal is an active low Schmitt-trigger input when configured

for the master mode but an active low output when configured for the slave mode.

When configured for the slave mode, HREQ is asserted to indicate that the SHI is

ready for the next data word transfer and deasserted at the first clock pulse of the

new data word transfer. When configured for the master mode, HREQ is an input.

When asserted by the external slave device, it will trigger the start of the data word

transfer by the master. After finishing the data word transfer, the master will await

the next assertion of HREQ to proceed to the next transfer.

This signal is tri-stated during hardware, software, personal reset, or when the

HREQ1–HREQ0 bits in the HCSR are cleared. There is no need for external pull-up

in this state.

This input is 3.3V tolerant.

2-12

DSP56367 Technical Data, Rev. 2.1

Freescale Semiconductor