EDS5104ABTA View Datasheet(PDF) - Elpida Memory, Inc

Part Name

Description

Manufacturer

EDS5104ABTA Datasheet PDF : 52 Pages

| |||

EDS5104ABTA, EDS5108ABTA, EDS5116ABTA

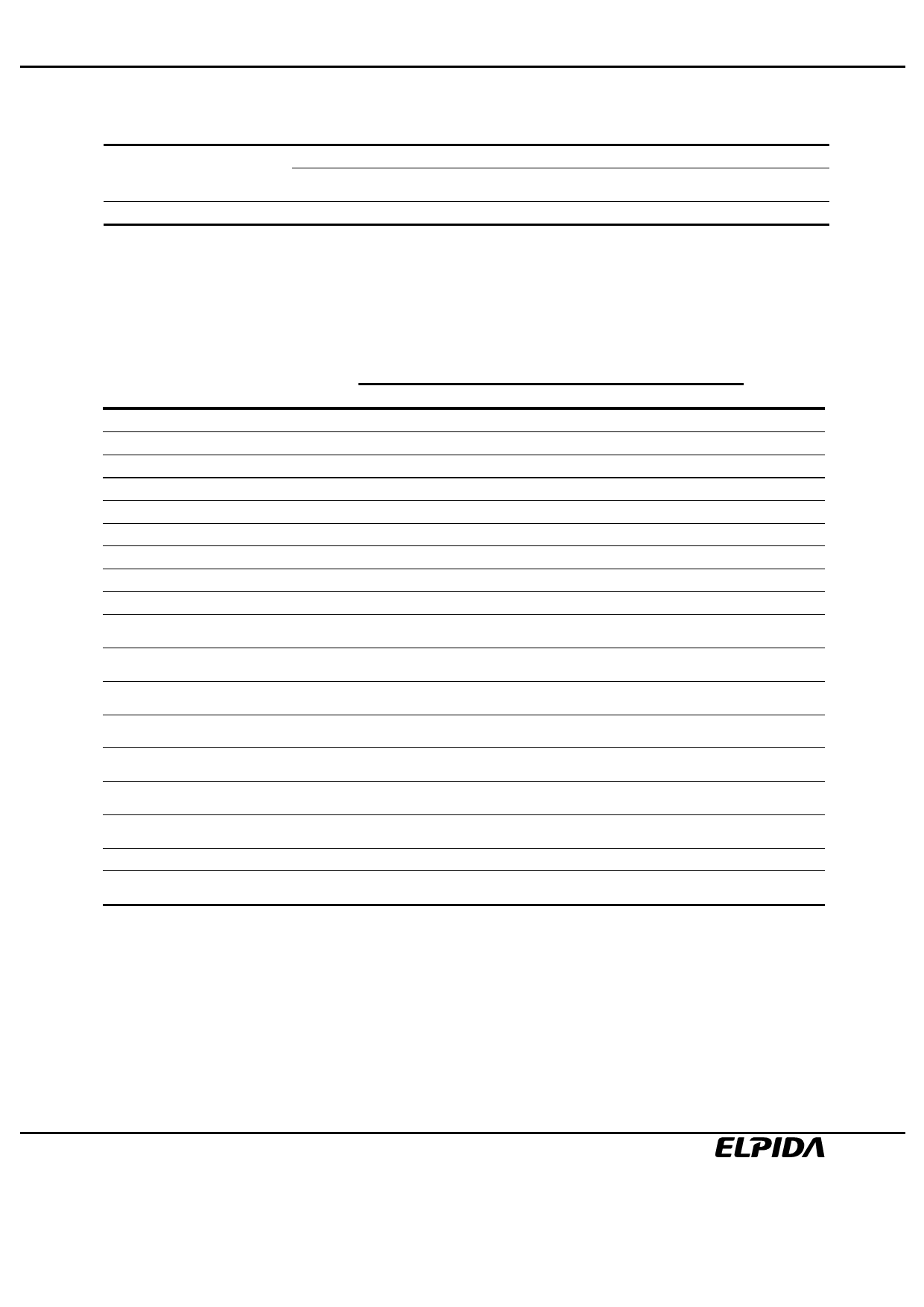

Pin Capacitance (TA = 25°C, VDD, VDDQ = 3.3V ± 0.3V)

Parameter

Symbol Pins

min.

Typ

max.

Unit

Input capacitance

CI1

CLK

2.5

—

CI2

Address, CKE, /CS, /RAS,

/CAS, /WE, DQM,

2.5

—

Data input/output capacitance CI/O

DQ

4

—

3.5

pF

3.8

pF

6.5

pF

Notes: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2. Measurement condition: f = 1MHz, 1.4V bias, 200mV swing.

3. DQM = VIH to disable DOUT.

4. This parameter is sampled and not 100% tested.

Notes

1, 2, 4

1, 2, 4

1, 2, 3, 4

AC Characteristics (TA = 0 to +70°C, VDD, VDDQ = 3.3V ± 0.3V, VSS, VSSQ = 0V)

-6B

-7A

-75

Parameter

Symbol min.

max.

min.

max.

min.

max.

Unit Notes

System clock cycle time

tCK

6.0

—

7.5

—

7.5

—

ns 1

CLK high pulse width

tCH

2.5

—

2.5

—

2.5

—

ns 1

CLK low pulse width

tCL

2.5

—

2.5

—

2.5

—

ns 1

Access time from CLK

tAC

—

5.0

—

5.4

—

5.4

ns 1, 2

Data-out hold time

tOH

2.5

—

3.0

—

3.0

—

ns 1, 2

CLK to Data-out low impedance tLZ

1

—

1

—

1

—

ns 1, 2, 3

CLK to Data-out high impedance tHZ

—

5.4

—

5.4

—

5.4

ns 1, 4

Input setup time

tSI

1.5

—

1.5

—

1.5

—

ns 1

Input hold time

tHI

0.8

—

0.8

—

0.8

—

ns 1

Ref/Active to Ref/Active command

period

tRC

60

—

60

—

67.5

—

ns 1

Active to Precharge command

period

Active command to column

command (same bank)

tRAS 42

tRCD 18

120000 45

—

15

120000 45

—

20

120000 ns 1

—

ns 1

Precharge to active command

period

tRP

18

—

15

—

20

—

ns 1

Write recovery or data-in to

precharge lead time

tDPL 12

—

15

—

15

—

ns 1

Last data into active latency

tDAL

2CLK +

18ns

—

Active (a) to Active (b) command

period

tRRD

12

—

2CLK +

15ns

—

15

—

2CLK +

20ns

—

15

—

ns 1

Transition time (rise and fall)

tT

0.5

5

0.5

5

0.5

5

ns

Refresh period

(8192 refresh cycles)

tREF —

64

—

64

—

64

ms

Notes: 1. AC measurement assumes tT = 0.5ns. Reference level for timing of input signals is 1.4V.

2. Access time is measured at 1.4V. Load condition is CL = 50pF.

3. tLZ (min.) defines the time at which the outputs achieves the low impedance state.

4. tHZ (max.) defines the time at which the outputs achieves the high impedance state.

Preliminary Data Sheet E0250E10 (Ver. 1.0)

6