9LPRS545BFLF View Datasheet(PDF) - Integrated Circuit Solution Inc

Part Name

Description

Manufacturer

9LPRS545BFLF Datasheet PDF : 17 Pages

| |||

Integrated

Circuit

Systems, Inc.

ICS9LPRS545

Datasheet

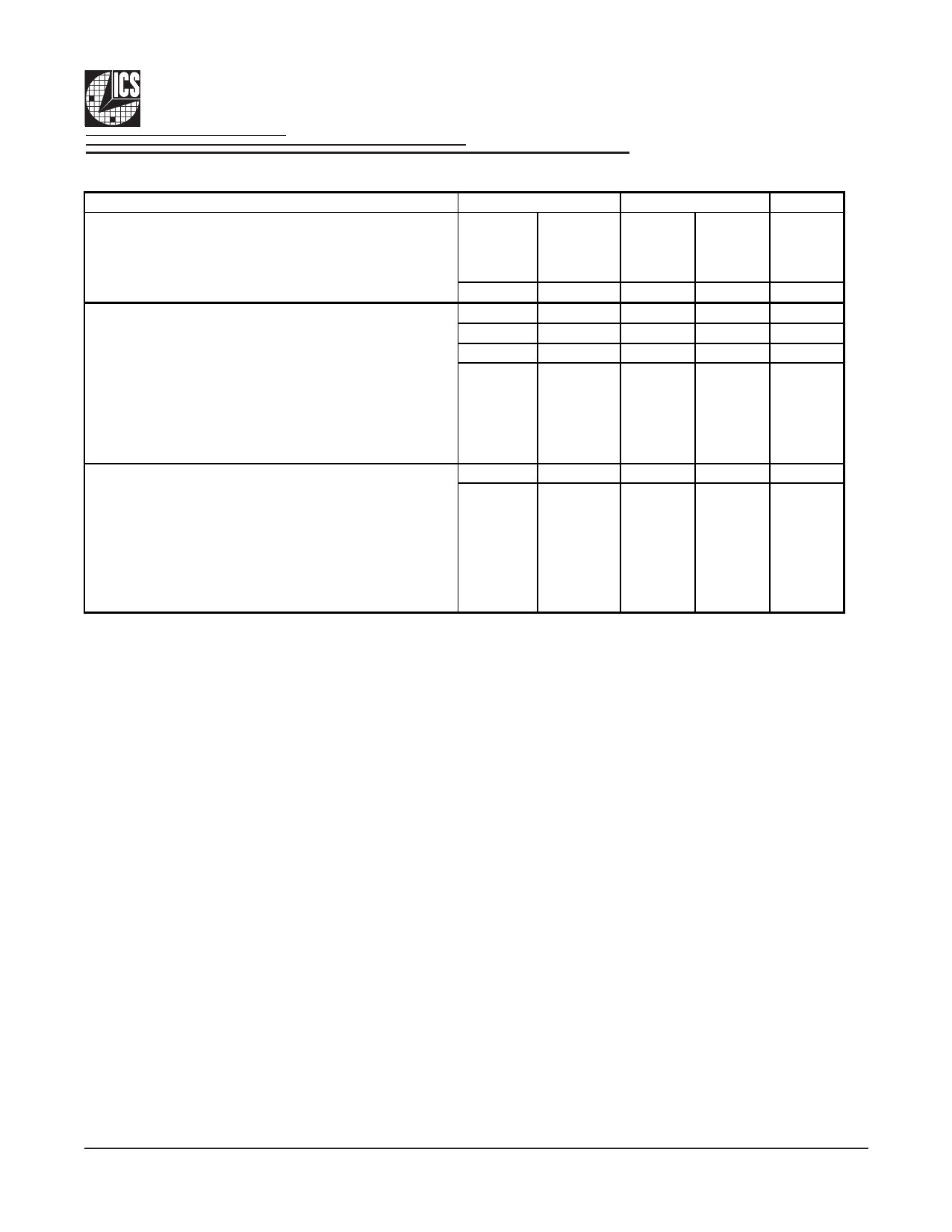

Test Clarification Table

Comments

Power-up w/ TEST_SEL = 1 to enter test mode

Cycle power to disable test mode

FSLC./TEST_SEL -->3-level latched input

If power-up w/ V>2.0V then use TEST_SEL

If power-up w/ V<2.0V then use FSLC

FSLB/TEST_MODE -->low Vth input

TEST_MODE is a real time input

If TEST_SEL HW pin is 0 during power-up,

test mode can be invoked through B9b3.

If test mode is invoked by B9b3, only B9b4

is used to select HI-Z or REF/N

FSLB/TEST_Mode pin is not used.

Cycle power to disable test mode, one shot control

HW

SW

FSLB/

FSLC/ TEST_MOD TEST REF/N or

TEST_SEL

E

ENTRY BIT HI-Z

HW PIN

HW PIN

B9b3

B9b4

<2.0V

X

0

0

>2.0V

0

X

0

>2.0V

0

X

1

>2.0V

1

X

0

OUTPUT

NORMAL

HI-Z

REF/N

REF/N

>2.0V

1

X

1

REF/N

<2.0V

X

1

0

HI-Z

<2.0V

X

1

1

REF/N

B9b3: 1= ENTER TEST MODE, Default = 0 (NORMAL OPERATION)

B9b4: 1= REF/N, Default = 0 (HI-Z)

1479A—07/28/09

14