IDT71256 View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT71256

IDT71256 Datasheet PDF : 9 Pages

| |||

IDT71256 S/L

CMOS STATIC RAM 256K (32K x 8-BIT)

MILITARY AND COMMERCIAL TEMPERATURE RANGES

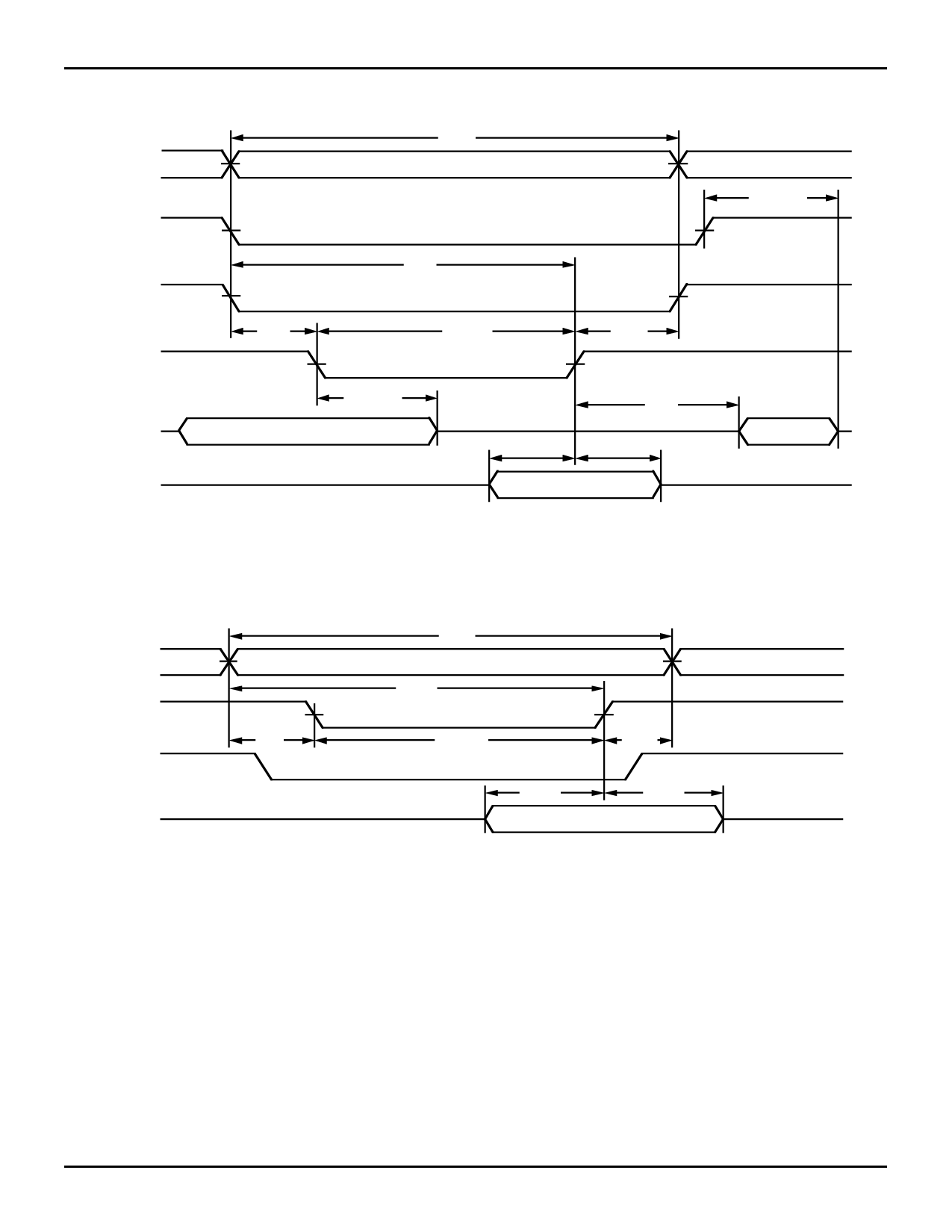

TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE CONTROLLED TIMING)(1, 2, 3, 5, 7)

ADDRESS

OE

CS

WE

DATA OUT

DATA IN

tWC

tAW

tAS

tWP (7)

tWHZ (6)

(4)

tDW

tWR

tOW

tDH

tOHZ (6)

(4)

2946 drw 10

TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CS CONTROLLED TIMING)(1, 2, 3, 5)

tWC

ADDRESS

tAW

CS

tAS

WE

tCW (7)

ttWR

tDW

tDH2

DATA IN

2946 drw 11

NOTES:

1. WE or CS must be HIGH during all address transitions.

2. A write occurs during the overlap of a LOW CS and a LOW WE.

3. tWR is measured from the earlier of CS or WE going HIGH to the end of the write cycle.

4. During this period, I/O pins are in the output state so that the input signals must not be applied.

5. If the CS LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state.

6. Transition is measured ±200mV from steady state.

7. If OE is LOW during a WE controlled write cycle, the write pulse width must be the larger of tWP or (tWHZ + tDW) to allow the I/O drivers to turn off and data

to be placed on the bus for the required tDW. If OE is HIGH during a WE controlled write cycle, this requirement does not apply and the write pulse can

be as short as the spectified tWP. For a CS controlled write cycle, OE may be LOW with no degradation to tCW.

7.2

8