IR1175 View Datasheet(PDF) - International Rectifier

Part Name

Description

Manufacturer

IR1175 Datasheet PDF : 9 Pages

| |||

IR1175

ADVANCE INFORMATION

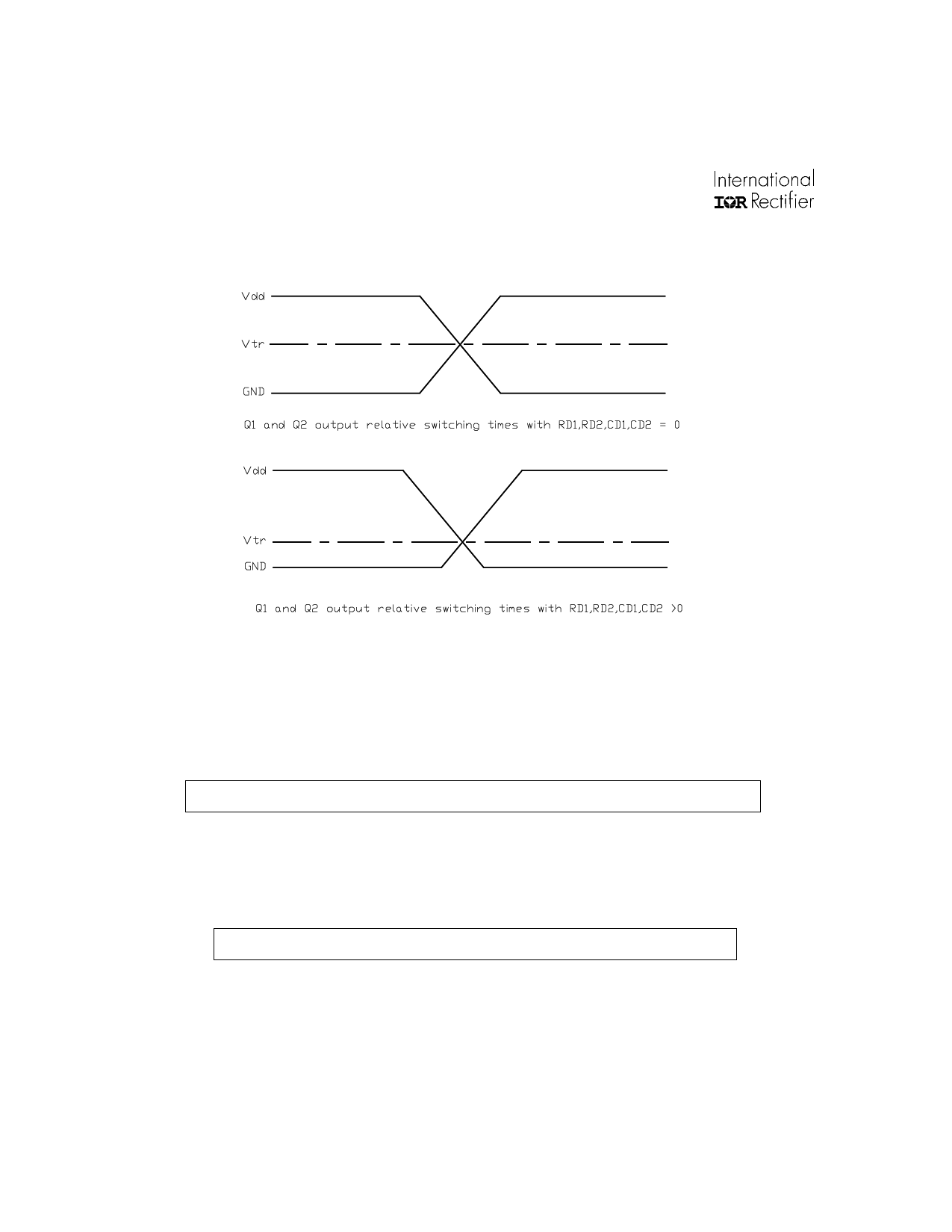

Fig. 3 Gate drive characteristics and definitions

Phase Lock Loop Design Equations:

1 - Resistor to set VCO Ceter Frequency:

Rvco (KW ) = 143 x [Vchgpump(VDC) / fvco(KHz)] x Kvco _ dc(KHz/mA)

Example (A): Choose Vchgpump = 1.5V, desired frequency (fvco) = 300KHz

Rvco = 143 x [1.5 /300] x 62 Hz/mA = 44.33 KW

2 - Small Signal gain for VCO:

Kvco_ac (KHz/Volt) = 1E3 x Kvco_dc (KHz/mA)/(7 x Rvco(KW )

Example (B): Choosing same conditions as in example A:

Kvco_ac = 1E3 x 62 / (7 x 44.33) = 199.9 KHz/volt

6

www.irf.com