LTC6907HS6 View Datasheet(PDF) - Linear Technology

Part Name

Description

Manufacturer

LTC6907HS6 Datasheet PDF : 12 Pages

| |||

LTC6907

APPLICATIO S I FOR ATIO

Alternative Methods for Setting the Output Frequency

Any means of sinking current from the SET pin will control

the output frequency of the LTC6907. Equation 2 (re-

peated below) gives the fundamental relationship between

frequency and the SET pin voltage and current:

tOSC

=

1

ƒOSC

=

VSET

ISET

• 5pF

(2)

This equation shows that the LTC6907 converts conduc-

tance (ISET/VSET) to frequency or, equivalently, converts

resistance (RSET = VSET/ISET) to period.

VSET is the voltage across an internal diode, and as such

it is given approximately by:

VSET

≅

VT

•

Loge

ISET

IS

≅

25.9mV

• Loge

⎛

⎝⎜

82

ISET

• 10–18

A

⎞

⎠⎟

– 2.3mV/ °C

where

VT = kT/q = 25.9mV at T = 300°K (27°C)

IS ≅ 82 • 10–18 Amps

(IS is also temperature dependent)

VSET varies with temperature and the SET pin current. The

response of VSET to temperature is shown in the Typical

Performance graphs. VSET changes approximately –2.3mV/

°C. At room temperature VSET increases 18mV/octave or

60mV/decade of increase in ISET.

If the SET pin is driven with a current source generating

ISET, the oscillator output frequency will be:

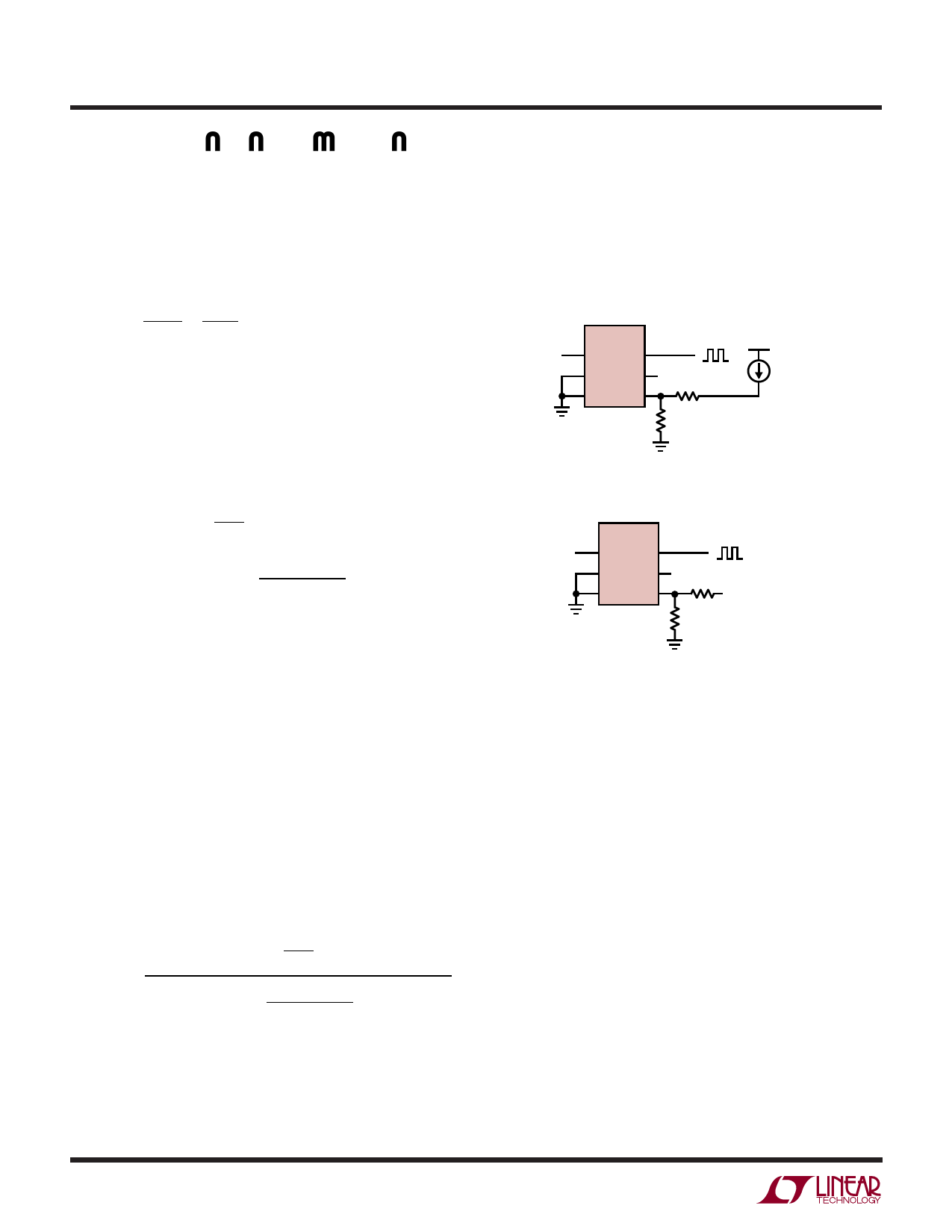

Figure 12 and Figure 13 show a current controlled oscilla-

tor and a voltage controlled oscillator. These circuits are

not highly accurate if used alone, but can be very useful if

they are enclosed in an overall feedback circuit such as a

phase-locked loop.

LTC6907

V+

V+ OUT

GND GRD

DIV SET

4MHz TO 400kHz

10k

0µA

TO 11.25µA

49.9k

6907 F12

Figure 12. Current Controlled Oscillator

LTC6907

V+

V+ OUT

4MHz TO 400kHz

GND GRD

DIV SET

499k

RSET

56.2k

VCTRL

0V TO 0.675V (VSET)

6907 F13

Figure 13. Voltage Controlled Oscillator

Jitter and Divide Ratio

At a given output frequency, a higher master oscillator

frequency and a higher divide ratio will result in lower jitter

and higher power supply dissipation. Indeterminate jitter

percentage will decrease by a factor of slightly less than

the square root of the divider ratio, while determinate jitter

will not be similarly attenuated. Please consult the speci-

fication tables for typical jitter at various divider ratios.

ISET

ƒOSC

≅

25.9mV

• Loge

⎛

⎝⎜

5pF

ISET

82 • 10–18

A

⎞

⎠⎟

– 2.3mV/°C

6907fa

10