M29W017D View Datasheet(PDF) - STMicroelectronics

Part Name

Description

Manufacturer

M29W017D Datasheet PDF : 36 Pages

| |||

M29W017D

BUS OPERATIONS

There are five standard bus operations that control

the device. These are Bus Read, Bus Write, Out-

put Disable, Standby and Automatic Standby. See

Tables 2, Bus Operations, for a summary. Typical-

ly glitches of less than 5ns on Chip Enable or Write

Enable are ignored by the memory and do not af-

fect bus operations.

Bus Read. Bus Read operations read from the

memory cells, or specific registers in the Com-

mand Interface. A valid Bus Read operation in-

volves setting the desired address on the Address

Inputs, applying a Low signal, VIL, to Chip Enable

and Output Enable and keeping Write Enable

High, VIH. The Data Inputs/Outputs will output the

value, see Figure 10, Read Mode AC Waveforms,

and Table 10, Read AC Characteristics, for details

of when the output becomes valid.

Bus Write. Bus Write operations write to the

Command Interface. A valid Bus Write operation

begins by setting the desired address on the Ad-

dress Inputs. The Address Inputs are latched by

the Command Interface on the falling edge of Chip

Enable or Write Enable, whichever occurs last.

The Data Inputs/Outputs are latched by the Com-

mand Interface on the rising edge of Chip Enable

or Write Enable, whichever occurs first. Output En-

able must remain High, VIH, during the whole Bus

Write operation. See Figures 11 and 12, Write AC

Waveforms, and Tables 11 and 12, Write AC

Characteristics, for details of the timing require-

ments.

Output Disable. The Data Inputs/Outputs are in

the high impedance state when Output Enable is

High, VIH.

Standby. When Chip Enable is High, VIH, the

memory enters Standby mode and the Data In-

puts/Outputs pins are placed in the high-imped-

ance state. To reduce the Supply Current to the

Standby Supply Current, ICC2, Chip Enable should

be held within VCC ± 0.2V. For the Standby current

level see Table 9, DC Characteristics.

During program or erase operations the memory

will continue to use the Program/Erase Supply

Current, ICC3, for Program or Erase operations un-

til the operation completes.

Automatic Standby. If CMOS levels (VCC ± 0.2V)

are used to drive the bus and the bus is inactive for

300ns or more the memory enters Automatic

Standby where the internal Supply Current is re-

duced to the Standby Supply Current, ICC2. The

Data Inputs/Outputs will still output data if a Bus

Read operation is in progress.

Special Bus Operations

Additional bus operations can be performed to

read the Electronic Signature and also to apply

and remove Block Protection. These bus opera-

tions are intended for use by programming equip-

ment and are not usually used in applications.

They require VID to be applied to some pins.

Electronic Signature. The memory has two

codes, the manufacturer code and the device

code, that can be read to identify the memory.

These codes can be read by applying the signals

listed in Tables 2, Bus Operations.

Block Protection and Blocks Unprotection.

Each block can be separately protected against

accidental Program or Erase. Protected blocks

can be unprotected to allow data to be changed.

There are two methods available for protecting

and unprotecting the blocks, one for use on pro-

gramming equipment and the other for in-system

use. Block Protect and Chip Unprotect operations

are described in Appendix C.

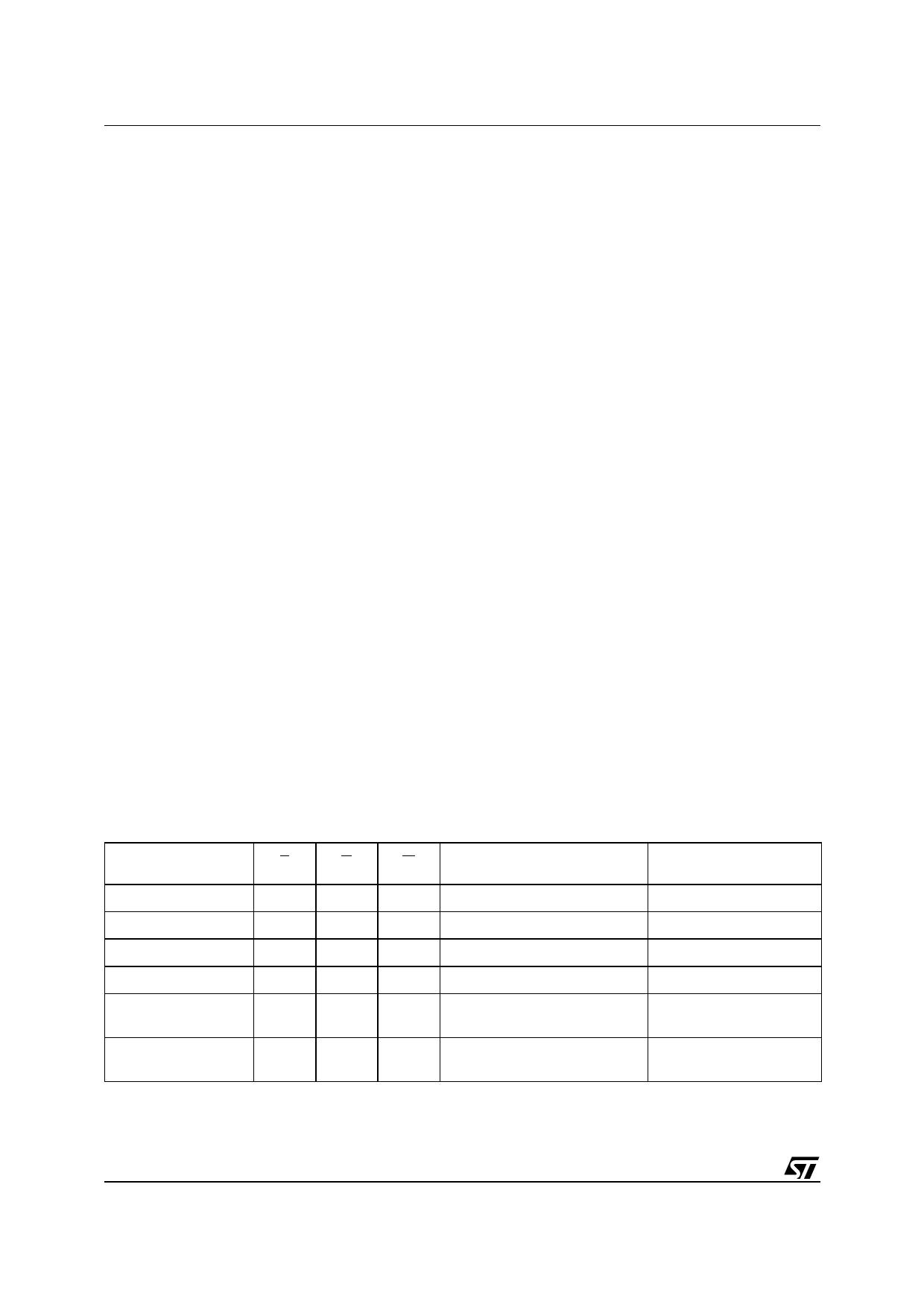

Table 2. Bus Operations

Operation

E

G

W

Address Inputs

A0-A20

Bus Read

VIL

VIL

VIH Cell Address

Bus Write

VIL

VIH

VIL Command Address

Output Disable

X

VIH

VIH X

Standby

VIH

X

XX

Read Manufacturer

Code

VIL

VIL

VIH

A0 = VIL, A1 = VIL, A9 = VID,

Others VIL or VIH

Read Device Code

Note: X = VIL or VIH.

VIL

VIL

VIH

A0 = VIH, A1 = VIL,

A9 = VID, Others VIL or VIH

Data Inputs/Outputs

DQ7-DQ0

Data Output

Data Input

Hi-Z

Hi-Z

20h

C8h

10/36