MC68322 View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MC68322 Datasheet PDF : 12 Pages

| |||

Freescale Semiconductor, Inc.

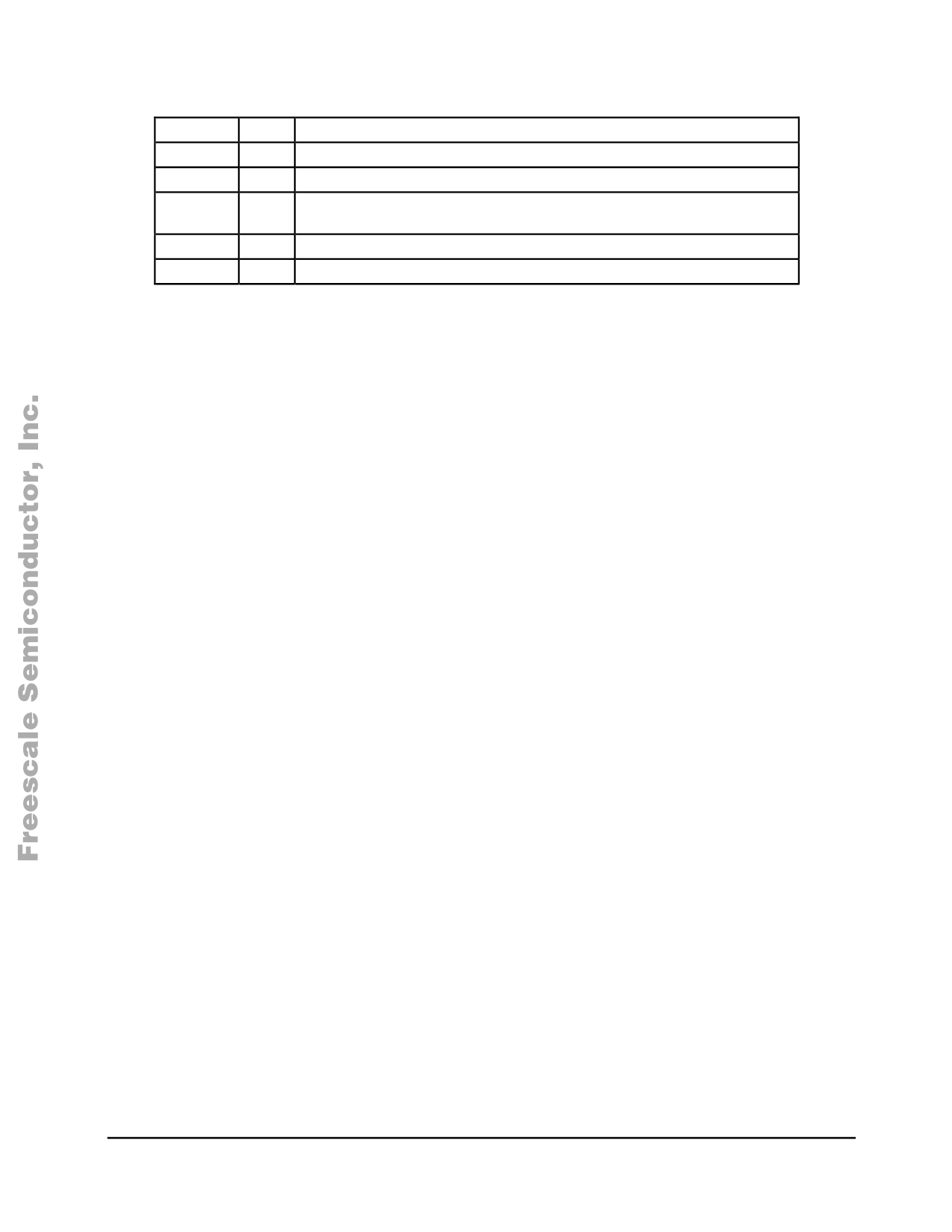

Signal

CBSY

SBSY

CMD/STS

STS

CCLK

Table 5. MC68322 Printer Communications Interface I/O Signals

I/O

Description

O Command busy indicates that a command will be sent to the printer.

I Status busy indicates the printer is ready to receive status.

I/O Command/Status Data is the synchronous command data out to the printer, or

the bi-directional command/status data to/from the printer.

I Status Data is the synchronous status data from the printer.

I/O Command Clock is the command/status clock to/from the printer.

The MC68322 contains two 8-bit registers for synchronous communications, a command register and a

status register. When the command register is written, the CBSY signal is brought active and the command

data is sent as a serial stream on the CMD line with CCLK toggling high-to-low and low-to-high once per

command bit. When the print engine is ready to respond with status, it does so by activating the SBSY

signal. This causes the MC68322 to toggle CCLK high-to-low and low-to-high eight times (once per status

bit) and assemble serial data from the STS line into the status register.

ON-CHIP PERIPHERALS

To improve total system throughput and reduce part count, board size, and cost of system implementation,

the M68300 family integrates on-chip, intelligent peripheral modules and typical glue logic. The MC68322

has five modules to assist the EC000 Core and GEU. These five modules are the bus interface unit (BIU),

system integration module (SIM), DRAM system integration module (DSIM), general purpose direct memory

access (DMA) controller, and parallel port interface (PPI).

BUS INTERFACE UNIT (BIU)

The dual bus architecture of the MC68322 allows the printing workload to be distributed among processing

units and executed in parallel. Because studies have shown that 70% of all MC68000 bus accesses are

instruction fetches, the MC68322 has been designed so that the EC000 Core bus traffic to DRAM is less

than 30% of all EC000 bus accesses.

The BIU allows the EC000 Core and GEU, which reside on separate bus structures, to function

independently by handling general purpose DMA, and EC000 Core accesses to DRAM. The EC000 Core

can perform instruction and PROM data fetches without impacting GEU bus operations. However, the GEU

has a higher priority than the EC000 Core for DRAM accesses in order to print pages correctly.

The BIU, in conjunction with the SIM, also allows SRAM to be added to the EC000 Core bus for system

stack space, temporary data storage, or as a buffer for peripheral data.

SYSTEM INTEGRATION MODULE

The SIM provides the ROM, PROM, and I/O chip selects. It contains eight chip selects that can be

programmed to decode the address and internally supply the DTACK after the appropriate number of wait

states. Each chip select can be programmed to support up to 64 Mbytes of address space.

CHIP-SELECT BANKS AND REGISTERS

The eight chip-selects directly support ROM, PROM and I/O chip-select banks. Each ROM or I/O bank is

pointed to by a corresponding chip-select register through the base address field. These eight chip-select

MOTOROLA

MC68322 PRODUCT INFORMATION

9

For More Information On This Product,

Go to: www.freescale.com