MC92303 View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MC92303 Datasheet PDF : 3 Pages

| |||

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Current Information@www.mot.com/ADC

Product Brief

QPSK/BPSK DIGITAL DEMODULATOR

MC92303

The MC92303 is a coherent digital demodulator for QPSK and BPSK modulated

signals utilized in Digital-TV applications according to the EBU defined DVB transmis-

sion standard for satellite Set-Top systems or similar. The MC92303 contains all the

functionality required to lock onto signals with frequency offsets as large as the baud

rate and extract the desired signal from a frequency band with adjacent channel inter-

ference and other undesirable signals.

Feature Summary

• DVB compliant QPSK/BPSK Coherent Demodulator

• Variable Modulation Rate up to 30 MBaud to work with all present European DVB

Channels

• Selectable Input Format (Offset Binary/2’s Complement)

• DC Offset Removal, I/Q-swapping and Input Format Selection in one block

• Decimation Filters for Oversampling Ratios of 2/T, 3/T, 4/T, 6/T, 8/T, 12/T and 16/T

• Half Nyquist Baseband Filters (α=0.35)

• Internal Numerically Controlled Oscillator (NCO)

• Automatic Gain Control (AGC) provided to analog front-end

• Automatic Frequency Control (AFC) to ±Rs (Symbol Rate)

• Clock Synchronization with 1-Bit Σ∆-Converter Output for ADC control

• Programmable Second Order Loop Filters for Carrier Recovery and AGC

• 3-bit Soft Decision output per Symbol with selectable format (Offset Binary/2’s

Complement/Sign Magnitude)

• Programmable Sampling Rates of the Digital Sigma-Delta Converters

• < 0.5 dB Implementation Loss from theory

• I2C Programmable Interface

• 0.5µ CMOS Process at 3.3V

RESET

CLK

I,Q[5:0]

CLK_VCO

FORMAT

VCO

AGC

Q_soft[2:0]

SDA

I_soft[2:0]

SADR[6:0]

SCL

Ordering Information

Device

Package

MC92303BT 160QFP

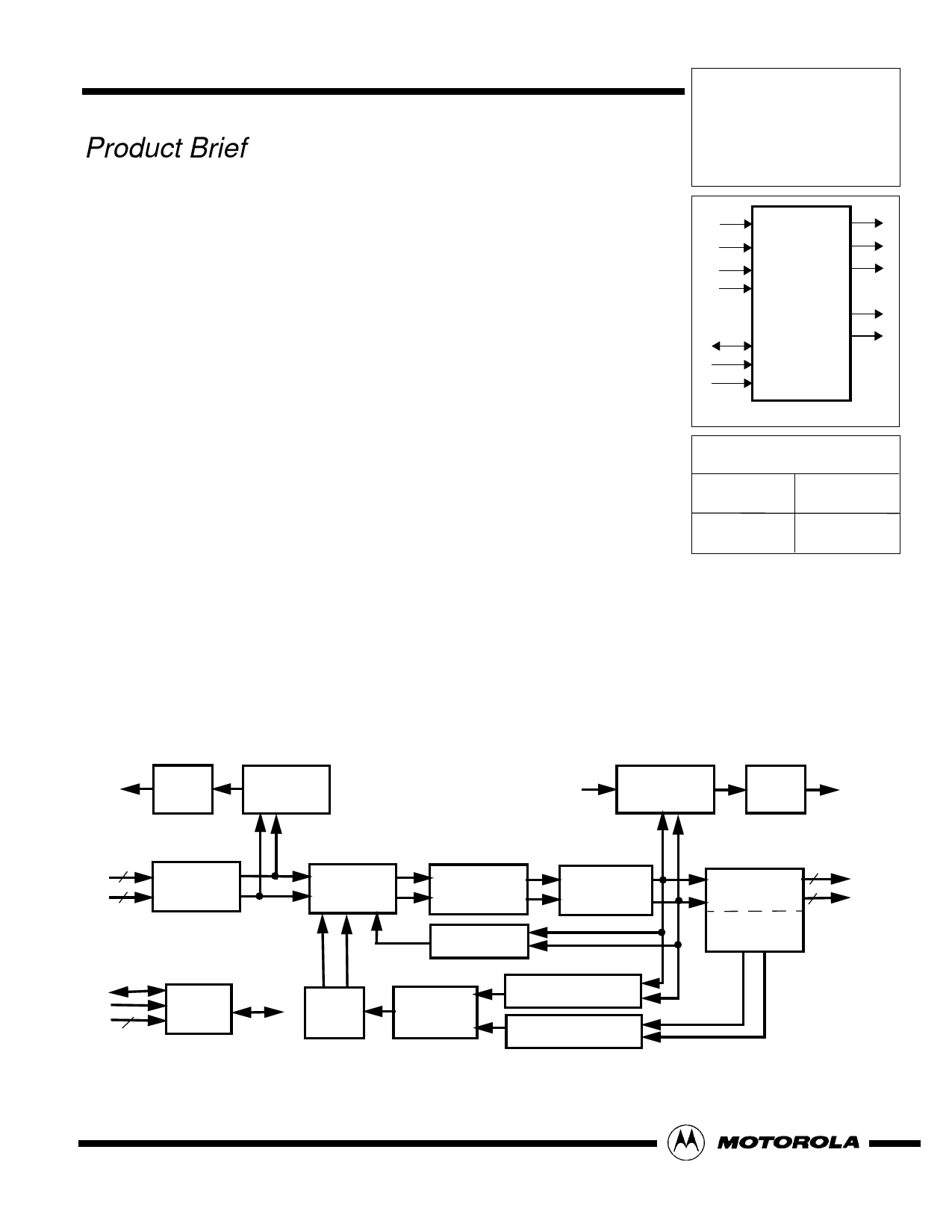

AGC

Σ∆

Control

AGC

Loop Filter

Ext. Clkref.

AFC / Clock

Synchron.

Σ∆

VCO

Control

I6

Q6

DC-

Removal

Complex

Multiplier

Decimation

Filter

Half Nyquist

Filter

Digital AGC

SDA

SCL 7

SADR

I2C

Interface

cosΘ

sinΘ

NCO

Parameters

Sweep /

Carrier

Loop Filter

False Lock Detector

Phase Lock Detector

Figure 1. QPSK/BPSK Demodulator Block Diagram

This document contains information on a new product.

Specifications and information herein are subject to change without notice.

3

8/3 Bit Mapper 3

Data

Estimator

© MOTOROLA, INC. 1997

I_soft

Q_soft

4/10/97