MCF5251(2007) View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

MCF5251 Datasheet PDF : 32 Pages

| |||

Functional Description

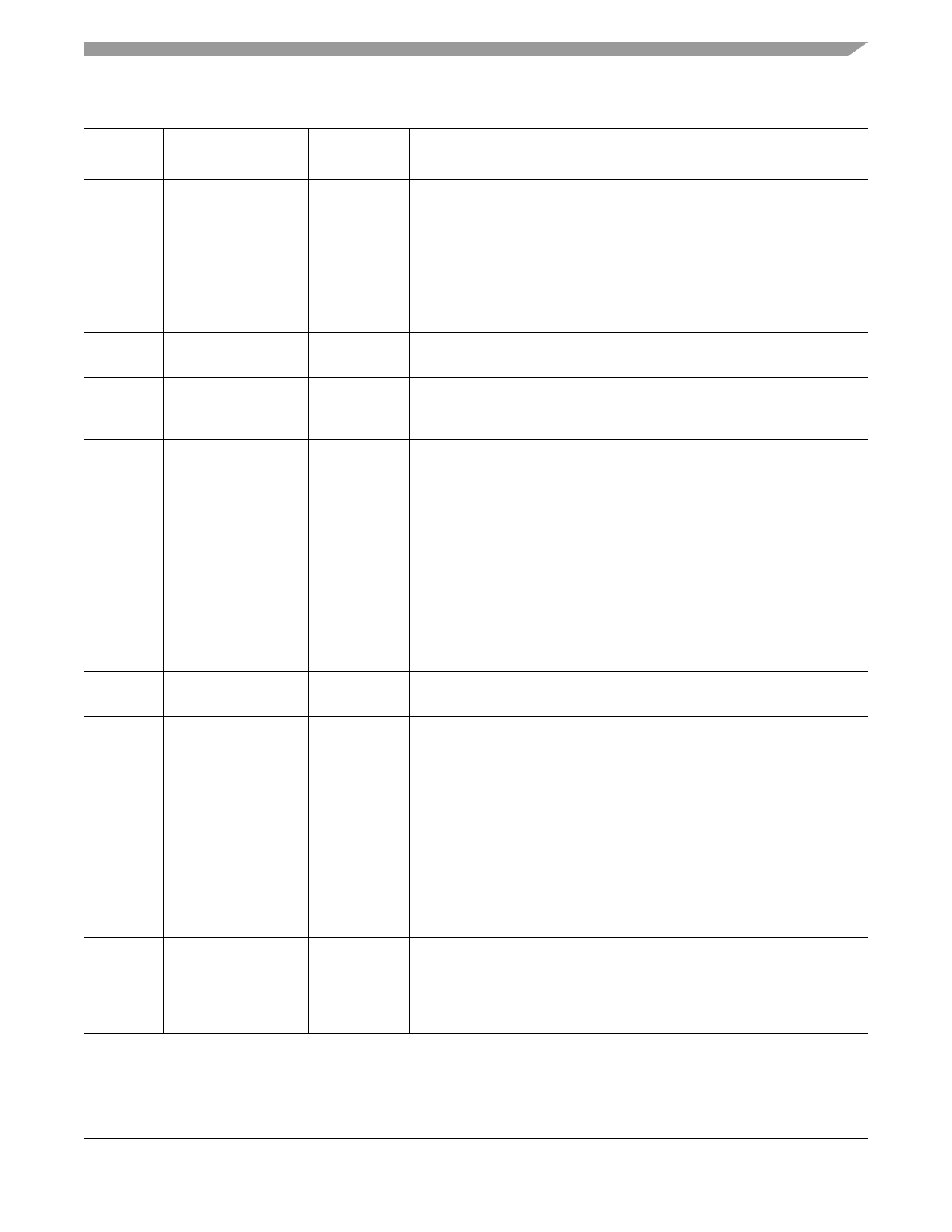

Table 2. Digital and Analog Modules (continued)

Block

Mnemonic

Block Name

Functional

Grouping

Brief Description

GPIO

GPT

IDE

INC

I2C

SRAM

LIN

JTAG

General Purpose I/O System

Interface

integration

General Timer

Module

Timer

peripheral

Integrated Drive

Electronics

Connectivity

peripheral

Instruction Cache

Core

Inter IC

Communication

Module

Internal 128-KB

SRAM

Internal Voltage

Regulator

Connectivity

peripheral

Internal

memory

Linear

regulator

Joint Test Action

Group

Test and

debug

QSPI

Queued Serial

Connectivity

Peripheral Interface Interface

RTC

Real-Time Clock

Timer

Peripheral

BDM

Background Debug Test and

Interface

debug

SDRAMC Synchronous DRAM Peripheral

Memory Controller Interface

SIM

System Integration System

Module

Integration

PLL

System Oscillator and System

Phase Lock Loop

Clocking

GPIO signals are multiplexed with various other signals.

The timer module includes two general-purpose timers, each of which

contains a free-running 16-bit timer.

The IDE hardware consists of bus buffers for address and data and are

intended to reduce the load on the bus and prevent SDRAM and Flash

accesses from propagating to the IDE bus.

The instruction cache improves system performance by providing cached

instructions to the execution unit in a single clock cycle.

The two-wire I2C bus interfaces, compliant with the Philips I2C bus

standard, are bidirectional serial buses that exchange data between

devices.

The 128-Kbyte on-chip SRAM is split over two banks, SRAM0 (64K) and

SRAM1 (64K). It provides single clock-cycle access for the ColdFire core.

An internal 1.2 V regulator is used to supply the CPU and PLL sections of

the MCF5251, reducing the number of external components required and

allowing operation from a single supply rail, typically 3.3 volts.

To help with system diagnostics and manufacturing testing, the MCF5251

includes dedicated user-accessible test logic that complies with the IEEE

1149.1A standard for boundary scan testability, often referred to as Joint

Test Action Group, or JTAG.

The QSPI module provides a serial peripheral interface with queued

transfer capability.

The RTC is a clock that keeps track of the current time even if the clock is

turned off.

A background-debug mode (BDM) interface provides system debug.

The SDRAM controller provides a glueless interface for one bank of

SDRAM, and can address up to 32MB. The controller supports a 16-bit

data bus. The controller operates in page mode, non-page mode, and

burst-page mode and supports SDRAMs.

The SIM provides overall control of the internal and external buses and

serves as the interface between the ColdFire core and the internal

peripherals or external devices. The SIM is responsible for the two

interrupt controllers (setting priorities and levels). And it also configures

the GPIO ports.

The oscillator operates from an external crystal connected across CRIN

and CROUT. The circuit can also operate from an external clock

connected to CRIN. The on-chip programmable PLL, which generates the

processor clock, allows the use of almost any low frequency external clock

(5вҖ“35 MHz).

MCF5253 ColdFire Processor Data Sheet: Technical Data, Rev. 2.2

Freescale Semiconductor

5