MPC7455 View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

MPC7455 Datasheet PDF : 64 Pages

| |||

Electrical and Thermal Characteristics

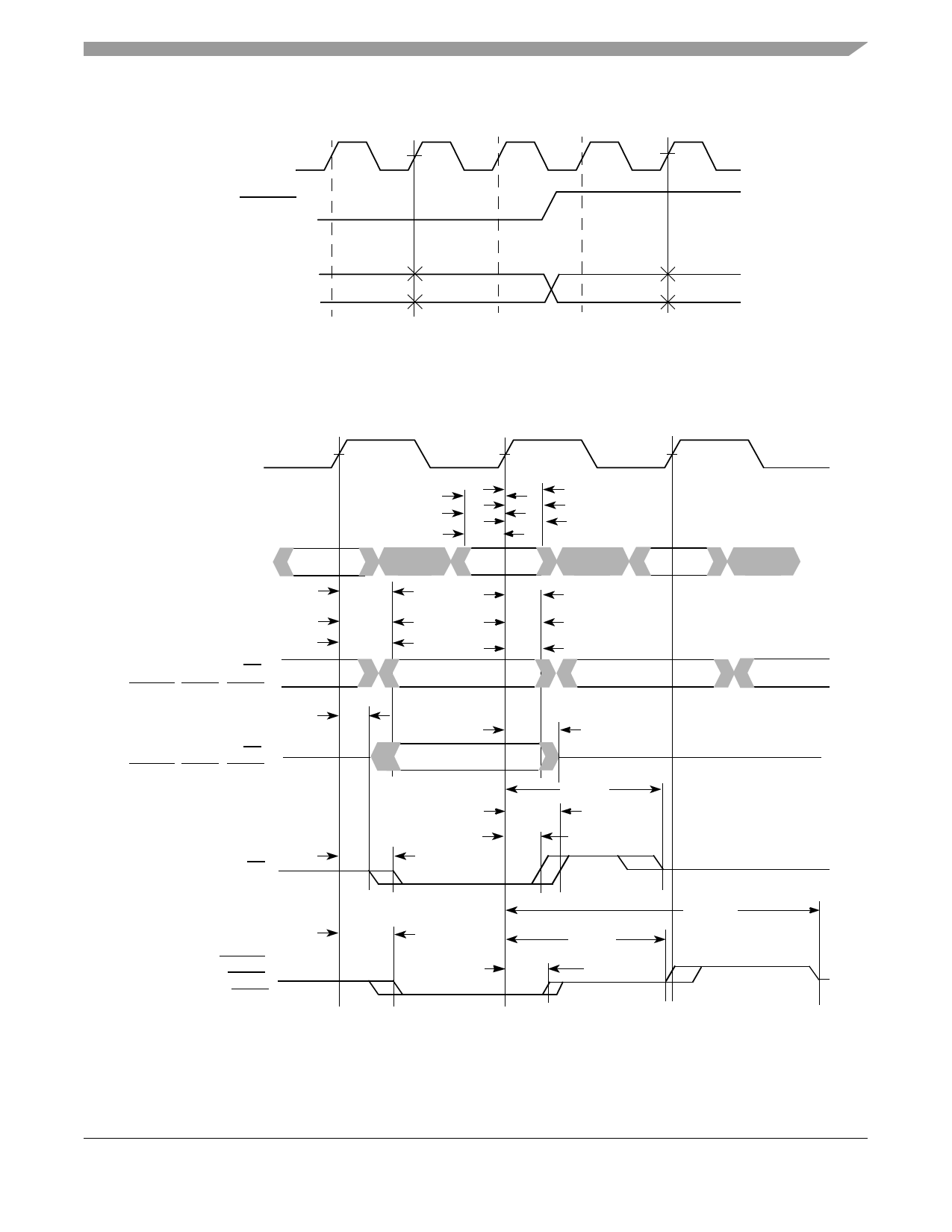

Figure 5 provides the mode select input timing diagram for the MPC7455.

SYSCLK

VM

VM

HRESET

Mode Signals

Firs t Sample

Second Sample

VM = Midpoint Voltage (OVDD/2)

Figure 5. Mode Input Timing Diagram

Figure 6 provides the input/output timing diagram for the MPC7455.

SYSCLK

VM

All Inputs

All Outputs

(Except TS,

ARTRY, SHD0, SHD1)

tKHOE

All Outputs

(Except TS,

ARTRY, SHD0, SHD1)

tAVKH

tIVKH

tMVKH

tKHAV

tKHDV

tKHOV

tKHTSV

TS

VM

tAXKH

tIXKH

tMXKH

tKHAX

tKHDX

tKHOX

tKHOZ

tKHTSPZ

tKHTSV

tKHTSX

ARTRY,

SHD0,

SHD1

tKHARV

tKHARP

tKHARX

VM = Midpoint Voltage (OVDD/2)

Figure 6. Input/Output Timing Diagram

VM

tKHARPZ

MPC7455 RISC Microprocessor Hardware Specifications, Rev. 4.1

Freescale Semiconductor

19