MPC8540(2004) View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

MPC8540 Datasheet PDF : 1302 Pages

| |||

Paragraph

Number

4.4.3.6

4.4.3.7

4.4.3.8

4.4.3.9

4.4.3.10

4.4.3.11

4.4.3.12

4.4.3.13

4.4.3.14

4.4.3.15

4.4.3.16

4.4.3.17

4.4.3.18

4.4.3.19

4.4.3.20

4.4.3.21

4.4.4

4.4.4.1

4.4.4.2

4.4.4.3

4.4.4.4

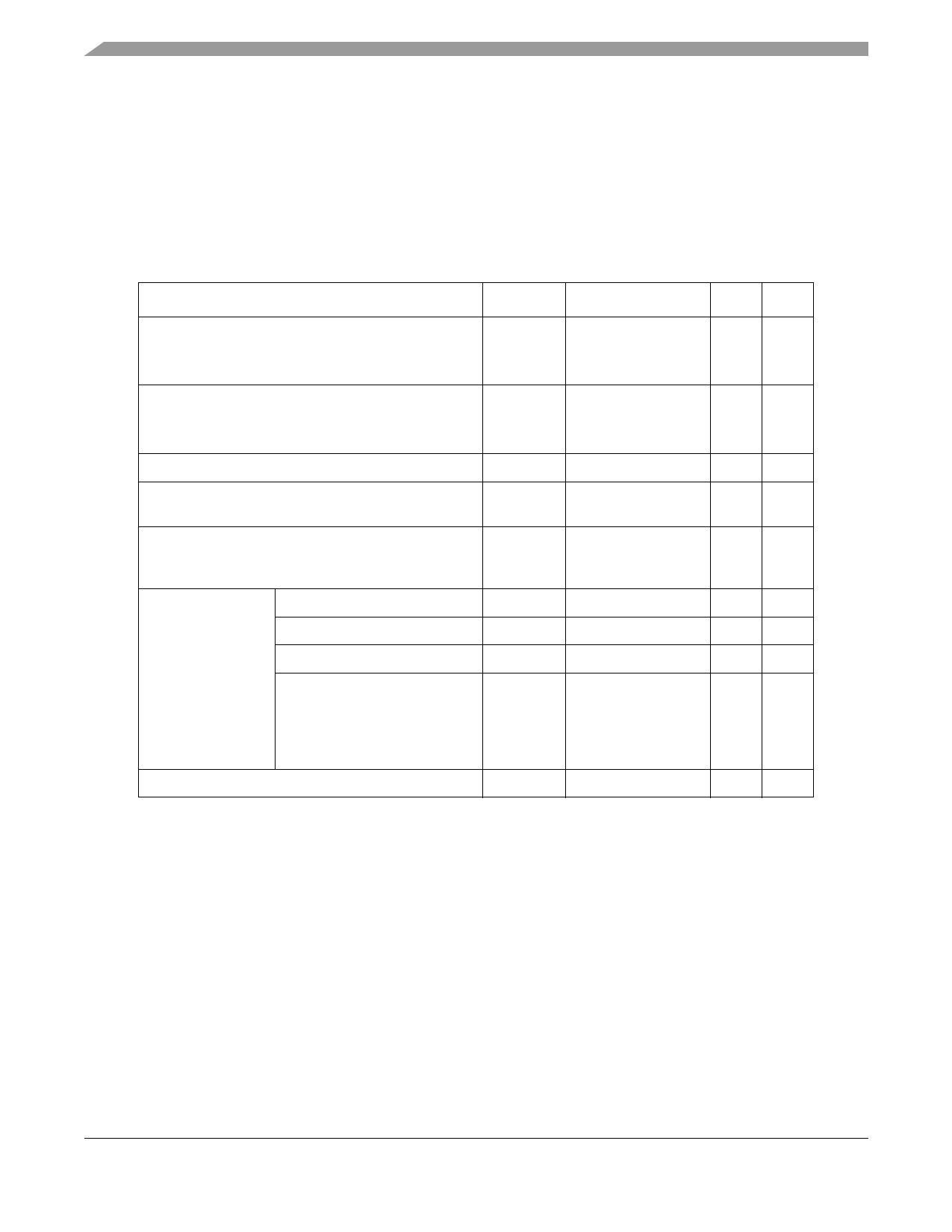

Contents

Title

Page

Number

Boot Sequencer Configuration .............................................................................. 4-16

TSEC Width........................................................................................................... 4-16

TSEC1 Protocol ..................................................................................................... 4-17

TSEC2 Protocol ..................................................................................................... 4-17

RapidIO Transmit Clock Source............................................................................ 4-18

RapidIO Device ID ................................................................................................ 4-18

PCI Width Configuration....................................................................................... 4-19

PCI I/O Impedance ................................................................................................ 4-19

PCI Arbiter Configuration ..................................................................................... 4-19

PCI Debug Configuration ...................................................................................... 4-20

PCI-X Configuration ............................................................................................. 4-20

Memory Debug Configuration .............................................................................. 4-20

DDR Debug Configuration.................................................................................... 4-21

PCI/PCI-X Output Hold Configuration ................................................................. 4-21

Local Bus Output Hold Configuration .................................................................. 4-22

General-Purpose POR Configuration .................................................................... 4-23

Clocking..................................................................................................................... 4-23

System Clock/PCI Clock ....................................................................................... 4-23

RapidIO Clocks ..................................................................................................... 4-24

Ethernet Clocks...................................................................................................... 4-25

Real Time Clock .................................................................................................... 4-25

Part II

e500 Core Complex and L2 Cache

5.1

5.1.1

5.1.2

5.2

5.3

5.4

5.5

5.5.1

5.5.2

5.5.3

5.6

5.7

Chapter 5

Core Complex Overview

Overview.......................................................................................................................... 5-1

Upward Compatibility ................................................................................................. 5-3

Core Complex Summary ............................................................................................. 5-3

e500 Processor and System Version Numbers................................................................. 5-4

Features ............................................................................................................................ 5-5

Instruction Set ................................................................................................................ 5-12

Instruction Flow ............................................................................................................. 5-14

Initial Instruction Fetch.............................................................................................. 5-14

Branch Detection and Prediction ............................................................................... 5-14

e500 Execution Pipeline ............................................................................................ 5-15

Programming Model ...................................................................................................... 5-18

On-Chip Cache Implementation .................................................................................... 5-20

MPC8540 PowerQUICC III Integrated Host Processor Reference Manual, Rev. 1

viii

Freescale Semiconductor