MPC9774 View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MPC9774 Datasheet PDF : 16 Pages

| |||

MPC9774

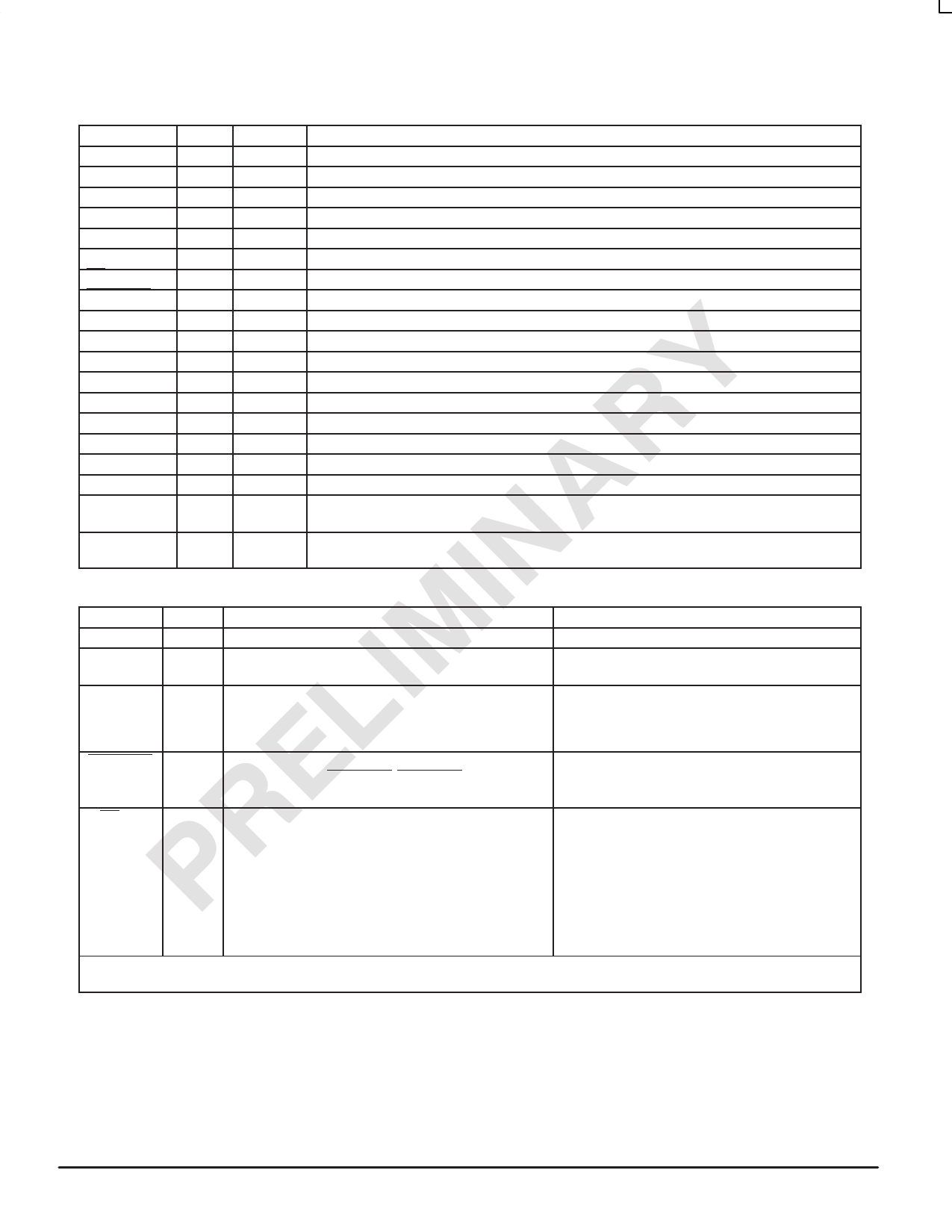

Table 1. PIN CONFIGURATION

Pin

I/O

Type

CCLK0

Input LVCMOS

CCLK1

Input LVCMOS

FB_IN

Input LVCMOS

CCLK_SEL

Input LVCMOS

VCO_SEL

Input LVCMOS

PLL_EN

Input LVCMOS

MR/OE

Input LVCMOS

CLK_STOP

Input LVCMOS

FSEL_A

Input LVCMOS

FSEL_B

Input LVCMOS

FSEL_C

Input LVCMOS

FSEL_FB[1:0] Input LVCMOS

QA[4:0]

Output LVCMOS

QB[4:0]

Output LVCMOS

QC[3:0]

Output LVCMOS

QFB

Output LVCMOS

GND

Supply Ground

VCC_PLL

Supply VCC

VCC

Supply VCC

Function

PLL reference clock

Alternative PLL reference clock

PLL feedback signal input, connect to QFB

LVCMOS clock reference select

VCO operating frequency select

PLL enable/PLL bypass mode select

Output enable/disable (high-impedance tristate) and device reset

Output enable/clock stop (logic low state)

Frequency divider select for bank A outputs

Frequency divider select for bank B outputs

Frequency divider select for bank C outputs

Frequency divider select for the QFB output

Clock outputs (Bank A)

Clock outputs (Bank B)

Clock outputs (Bank C)

PLL feedback output. Connect to FB_IN.

Negative power supply

PLL positive power supply (analog power supply). It is recommended to use an external RC filter

for the analog power supply pin VCC_PLL. Please see applications section for details.

Positive power supply for I/O and core. All VCC pins must be connected to the positive power

supply for correct operation

Table 2. Function Table (MPC9774 configuration controls)

Control Default

0

CCLK_SEL

0

Selects CCLK0 as PLL refererence signal input

VCO_SEL

0

Selects VCO ÷ 2. The VCO frequency is scaled by a

factor of 2 (high input frequency range)

1

Selects CCKL1 as PLL reference signal input

Selects VCO ÷ 4. The VCO frequency is scaled by a

factor of 4 (low input frequency range).

PLL_EN

1

Test mode with the PLL bypassed. The reference clock is Normal operation mode with PLL enabled.

substituted for the internal VCO output. MPC9774 is fully

static and no minimum frequency limit applies. All PLL

related AC characteristics are not applicable.

CLK_STOP

1

QA, QB an QC outputs disabled in logic low state. QFB Outputs enabled (active)

is not affected by CLK_STOP. CLK_STOP deassertion

may cause the initial output clock pulse to be distorted.

MR/OE

1

Outputs disabled (high-impedance state) and reset of the Outputs enabled (active)

device. During reset/output disable the PLL feedback

loop is open and the internal VCO is tied to its lowest

frequency. The MPC9774 requires reset after any loss of

PLL lock. Loss of PLL lock may occur when the external

feedback path is interrupted. The length of the reset

pulse should be greater than one reference clock cycle

(CCLKx). The device is reset by the internal power–on

reset (POR) circuitry during power–up.

VCO_SEL, FSEL_A, FSEL_B, FSEL_C and FSEL_FB[1:0] control the operating PLL frequency range and input/output frequency ratios.

See Table 3 and Table 4 for the device frequency configuration.

TIMING SOLUTIONS

3

MOTOROLA