MT48LC1M16A1 View Datasheet(PDF) - Micron Technology

Part Name

Description

Manufacturer

MT48LC1M16A1 Datasheet PDF : 51 Pages

| |||

COMMANDS

Truth Table 1 provides a quick reference of available

commands. This is followed by a written description of

each command. Three additional Truth Tables appear

16Mb: x16

IT SDRAM

following the Operation section; these tables provide

current state/next state information.

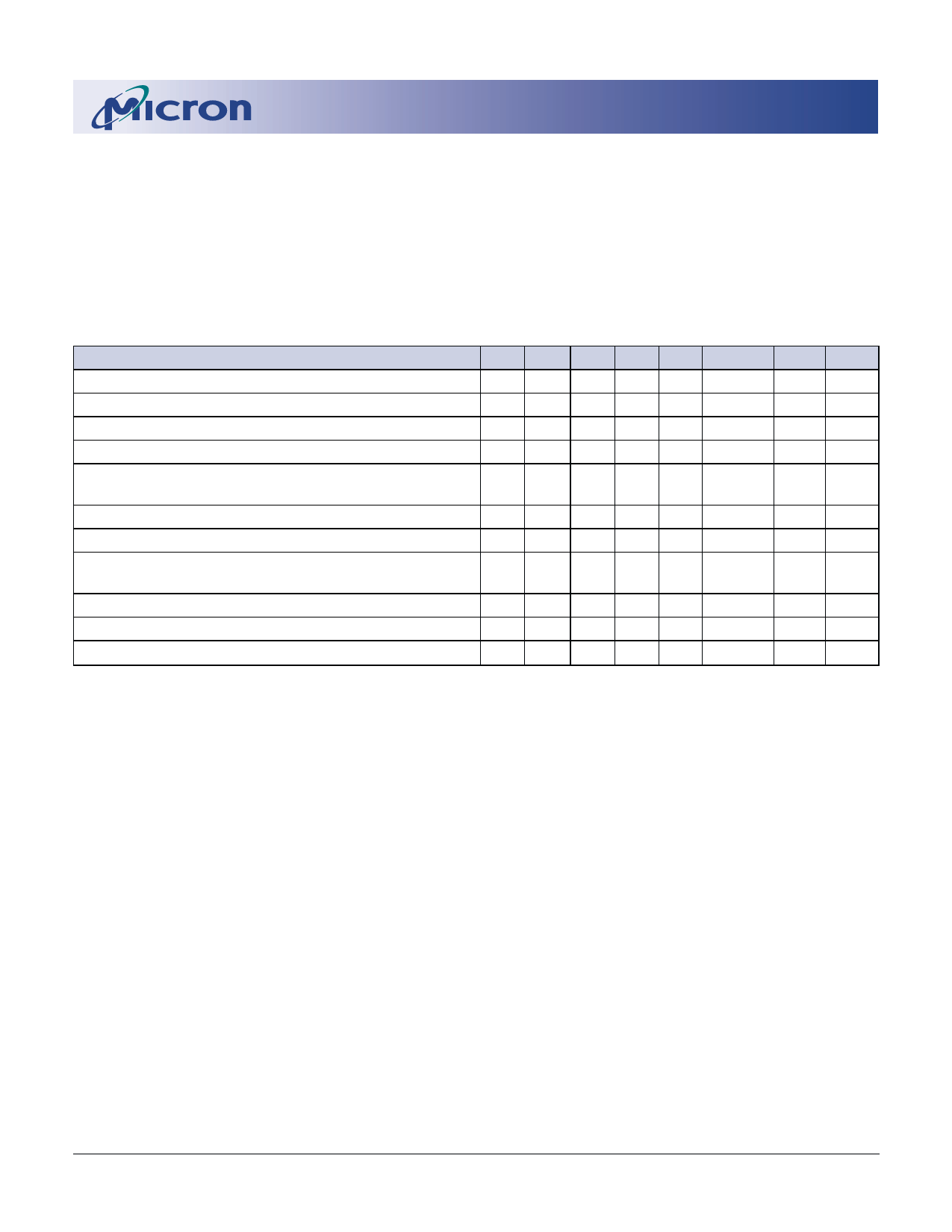

TRUTH TABLE 1 – COMMANDS AND DQM OPERATION

(Notes: 1)

NAME (FUNCTION)

COMMAND INHIBIT (NOP)

NO OPERATION (NOP)

ACTIVE (Select bank and activate row)

READ (Select bank and column and start READ burst)

WRITE (Select bank and column and

start WRITE burst)

BURST TERMINATE

PRECHARGE (Deactivate row in bank or banks)

AUTO REFRESH or

SELF REFRESH (Enter self refresh mode)

LOAD MODE REGISTER

Write Enable/Output Enable

Write Inhibit/Output High-Z

CS# RAS# CAS# WE# DQM ADDR DQs NOTES

H X X XX

X

X

L HHHX

X

X

L L H H X Bank/Row X

3

L H L H L/H8 Bank/Col X

4

L

H

L

L L/H8 Bank/Col Valid 4

L HH LX

X Active

L L H L X Code

X

5

L L L HX

X

X 6, 7

L L L L X Op-Code X

2

– – – –L

– Active 8

– – – –H

– High-Z 8

NOTE:

1. CKE is HIGH for all commands shown except SELF REFRESH.

2. A0-A10 and BA define the op-code written to the Mode Register.

3. A0-A10 provide row address, and BA determines which bank is made active.

4. A0-A7 provide column address; A10 HIGH enables the auto precharge feature (nonpersistent), while A10 LOW disables

the auto precharge feature; BA determines which bank is being read from or written to.

5. For A10 LOW, BA determines which bank is being precharged; for A10 HIGH, all banks are precharged and BA is a

“Don’t Care.”

6. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

7. Internal refresh counter controls row addressing; all inputs and I/Os are “Don’t Care” except for CKE.

8. Activates or deactivates the DQs during WRITEs (zero-clock delay) and READs (two-clock delay).

16Mb: x16 IT SDRAM

16MSDRAMx16IT.p65 – Rev. 5/99

9

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©1999, Micron Technology, Inc.