M27W800 View Datasheet(PDF) - STMicroelectronics

Part Name

Description

Manufacturer

M27W800 Datasheet PDF : 15 Pages

| |||

M27W800

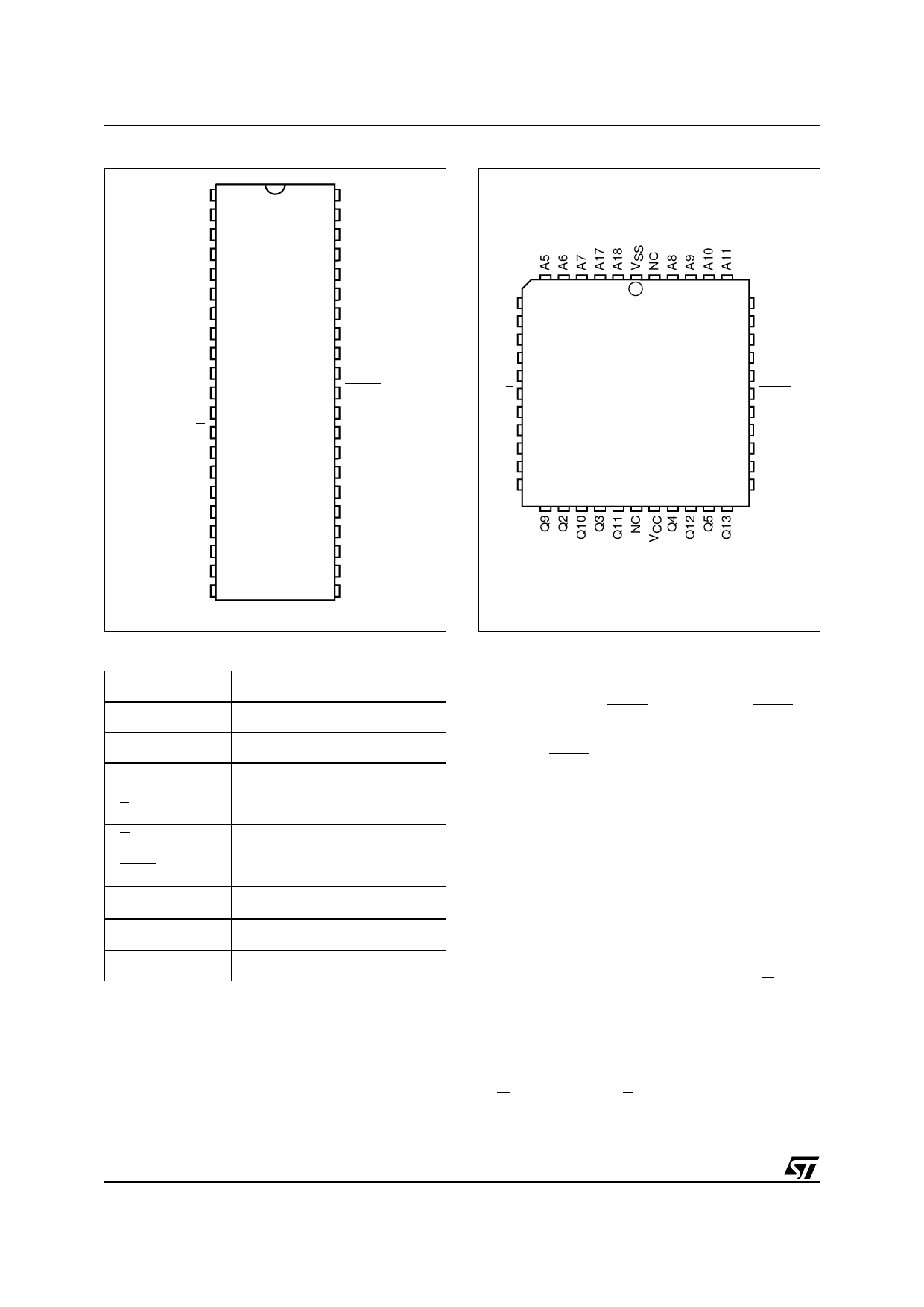

Figure 2A. DIP Connections

A18

A17

A7

A6

A5

A4

A3

A2

A1

A0

E

VSS

G

Q0

Q8

Q1

Q9

Q2

Q10

Q3

Q11

1

42 NC

2

41 A8

3

40 A9

4

39 A10

5

38 A11

6

37 A12

7

36 A13

8

35 A14

9

34 A15

10

33

M27W800

11

32

12

31

13

30

A16

BYTEVPP

VSS

Q15A-1

14

29 Q7

15

28 Q14

16

27 Q6

17

26 Q13

18

25 Q5

19

24 Q12

20

23 Q4

21

22 VCC

AI03602

Figure 2B. LCC Connections

A4

A3

A2

A1

A0

E 12

VSS

G

Q0

Q8

Q1

1 44

M27W800

23

A12

A13

A14

A15

A16

34 BYTEVPP

VSS

Q15A–1

Q7

Q14

Q6

AI03603

Table 1. Signal Names

A0-A18

Address Inputs

Q0-Q7

Data Outputs

Q8-Q14

Data Outputs

Q15A–1

Data Output / Address Input

E

Chip Enable

G

Output Enable

BYTEVPP

Byte Mode / Program Supply

VCC

Supply Voltage

VSS

Ground

NC

Not Connected Internally

DEVICE OPERATION

The operating modes of the M27W800 are listed in

the Operating Modes Table. A single power supply

is required in the read mode. All inputs are TTL

compatible except for VPP and 12V on A9 for the

Electronic Signature.

Read Mode

The M27W800 has two organisations, Word-wide

and Byte-wide. The organisation is selected by the

signal level on the BYTEVPP pin. When BYTEVPP

is at VIH the Word-wide organisation is selected

and the Q15A–1 pin is used for Q15 Data Output.

When the BYTEVPP pin is at VIL the Byte-wide or-

ganisation is selected and the Q15A–1 pin is used

for the Address Input A–1. When the memory is

logically regarded as 16 bit wide, but read in the

Byte-wide organisation, then with A–1 at VIL the

lower 8 bits of the 16 bit data are selected and with

A–1 at VIH the upper 8 bits of the 16 bit data are

selected.

The M27W800 has two control functions, both of

which must be logically active in order to obtain

data at the outputs. In addition the Word-wide or

Byte-wide organisation must be selected.

Chip Enable (E) is the power control and should be

used for device selection. Output Enable (G) is the

output control and should be used to gate data to

the output pins independent of device selection.

Assuming that the addresses are stable, the ad-

dress access time (tAVQV) is equal to the delay

from E to output (tELQV). Data is available at the

output after a delay of tGLQV from the falling edge

of G, assuming that E has been low and the ad-

dresses have been stable for at least tAVQV-tGLQV.

2/15