TDA8785H View Datasheet(PDF) - Philips Electronics

Part Name

Description

Manufacturer

TDA8785H

TDA8785H Datasheet PDF : 24 Pages

| |||

Philips Semiconductors

8-bit high-speed analog-to-digital converter

with gain and offset controls

Product specification

TDA8785

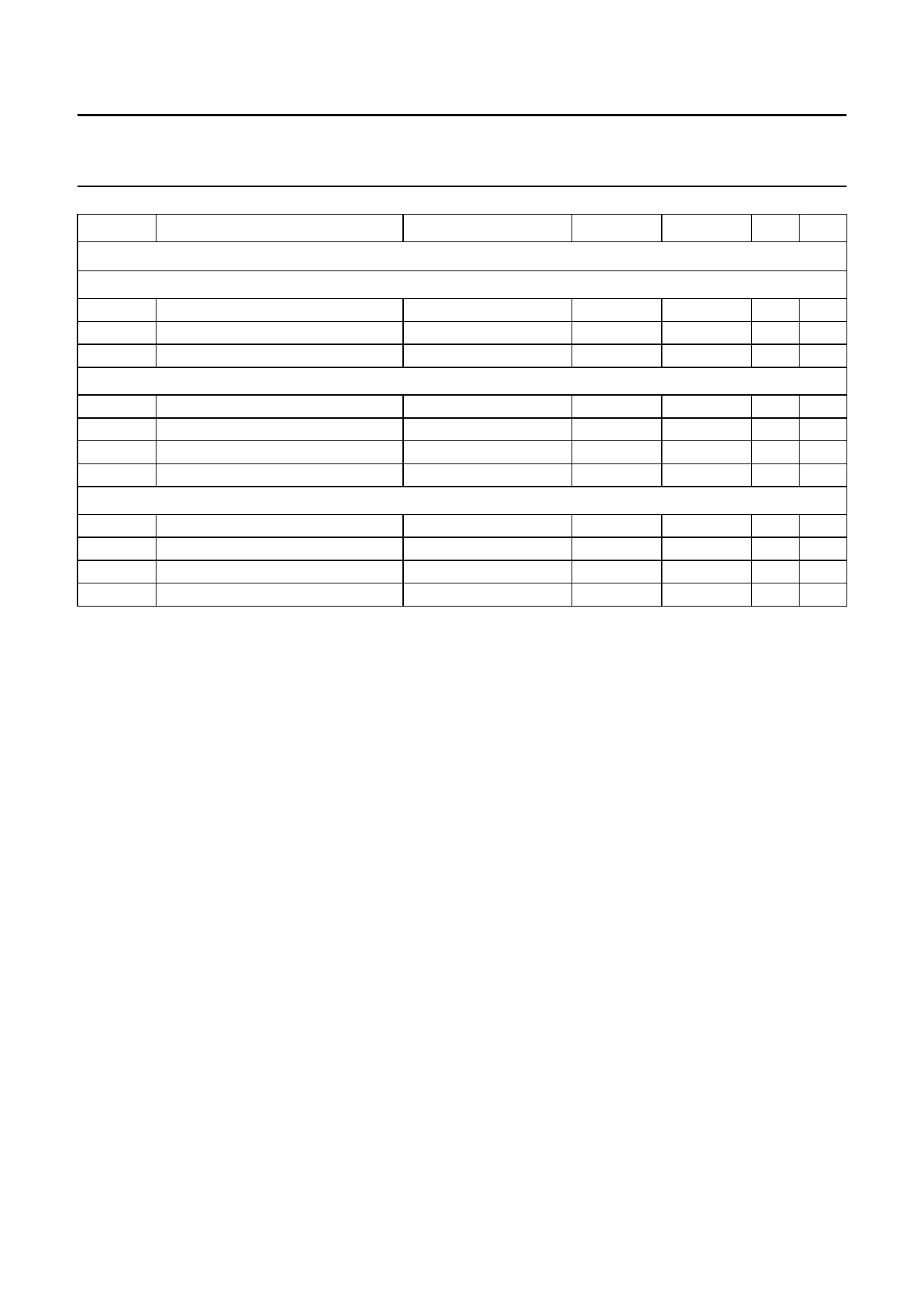

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP. MAX. UNIT

Timing

ADC DIGITAL OUTPUTS (CL = 15 pF)

tds

sampling delay time

th

output hold time

td

output delay time

−

1.5

−

ns

7

−

−

ns

−

−

16 ns

DAC OUTPUTS (PINS VDACO(p) AND VDACO(n))

tSU; DAT data set-up time

note 4

−0.3

−

tHD; DAT data hold time

note 4

−

−

tS

DAC setting time (10 to 90%)

RL = 150 Ω; CL = 15 pF −

8

RSA

residual setting accuracy

note 5; see Fig.8

0.1

−

ns

2

ns

−

ns

2.5 %

3-STATE OUTPUT DELAY TIMES (see Fig.5)

tdZH

enable HIGH

tdZL

enable LOW

tdHZ

disable HIGH

tdLZ

disable LOW

−

15

20 ns

−

15

20 ns

−

13

20 ns

−

10

20 ns

Notes

1. Vos is proportional to the amplifier gain. For instance, Vos at 20 dB is the one indicated at 0 dB multiplied by 10.

2. It is recommended that the rise and fall times of the clock are >1 ns. In addition a good layout for the digital and

analog grounds is recommended.

3. Analog processing from signal inputs or fast offset amplifier inputs to ADC digital output; fclk = 30 MHz; no external

filtering on pin 6 (B).

4. The data set-up time (tSU; DAT) is the minimum period preceding the rising edge of the clock, that the input data must

be stable in order to be correctly registered. A negative set-up time indicates that the data may be initiated after the

rising edge and still be recognized. The data set hold time (tHD; DAT) is the minimum period following the rising edge

of the clock, that the input data must be stable in order to be correctly registered. A negative hold time indicates that

the data may be released prior to the rising edge and still be recognized.

5. The residual settling accuracy is defined as follows. When a full-scale step is applied to the DAC, the initial settling

shows a fast settling behaviour. For the final part, the DAC analog output shows a slow settling behaviour.

The Residual Settling Accuracy (RSA) is defined as the full-scale error at the cross-over point at time tX.

1997 Dec 18

11