ATMEGA103 View Datasheet(PDF) - Atmel Corporation

Part Name

Description

Manufacturer

ATMEGA103 Datasheet PDF : 10 Pages

| |||

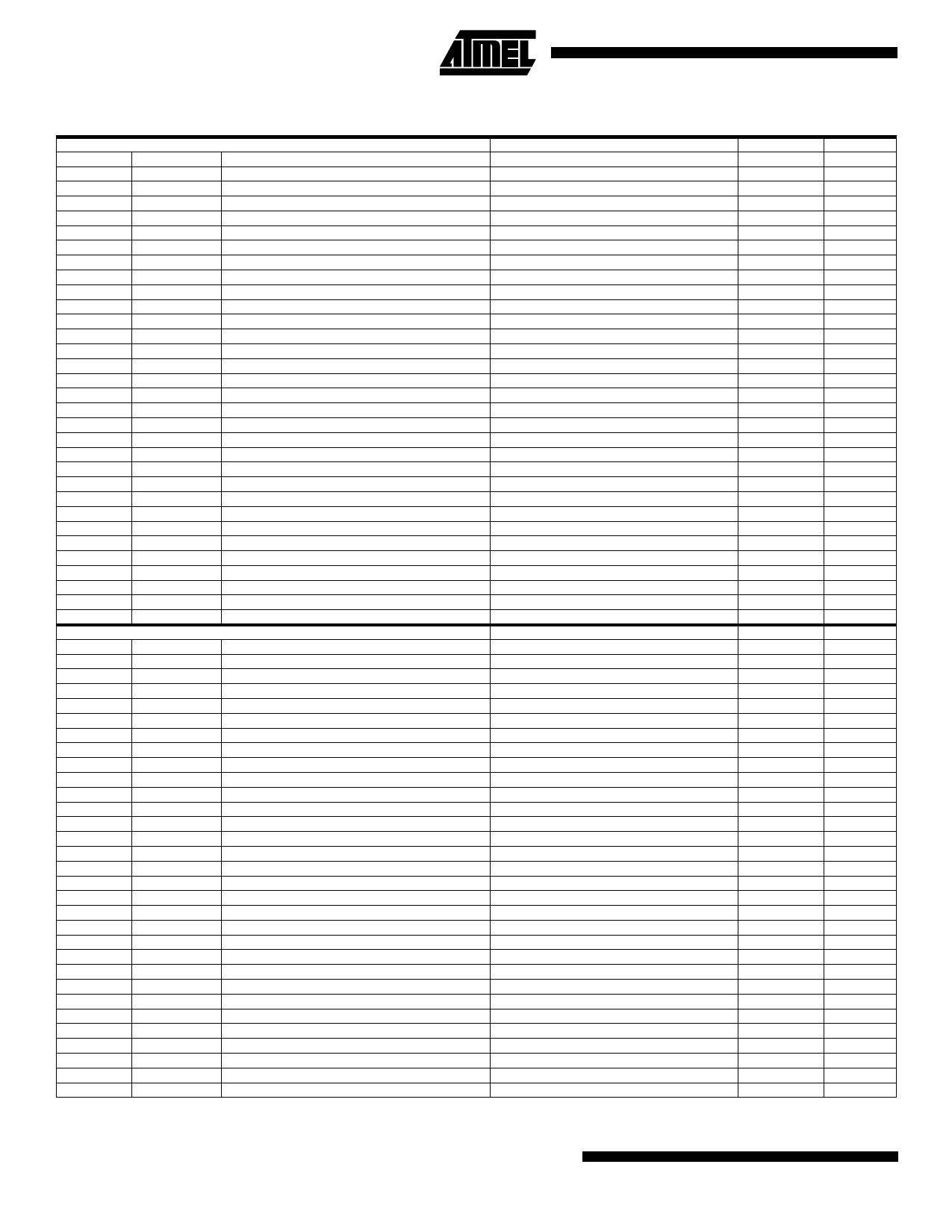

ATmega603/103 Instruction Set Summary (Continued)

DATA TRANSFER INSTRUCTIONS

ELPM()

MOV

Rd, Rr

LDI

Rd, K

LD

Rd, X

LD

Rd, X+

LD

Rd, - X

LD

Rd, Y

LD

Rd, Y+

LD

Rd, - Y

LDD

Rd,Y+q

LD

Rd, Z

LD

Rd, Z+

LD

Rd, -Z

LDD

Rd, Z+q

LDS

Rd, k

ST

X, Rr

ST

X+, Rr

ST

- X, Rr

ST

Y, Rr

ST

Y+, Rr

ST

- Y, Rr

STD

Y+q,Rr

ST

Z, Rr

ST

Z+, Rr

ST

-Z, Rr

STD

Z+q,Rr

STS

k, Rr

LPM

IN

Rd, P

OUT

P, Rr

PUSH

Rr

POP

Rd

BIT AND BIT-TEST INSTRUCTIONS

SBI

P,b

CBI

P,b

LSL

Rd

LSR

Rd

ROL

Rd

ROR

Rd

ASR

Rd

SWAP

Rd

BSET

s

BCLR

s

BST

Rr, b

BLD

Rd, b

SEC

CLC

SEN

CLN

SEZ

CLZ

SEI

CLI

SES

CLS

SEV

CLV

SET

CLT

SEH

CLH

NOP

SLEEP

WDR

Extended Load Program Memory

Move Between Registers

Load Immediate

Load Indirect

Load Indirect and Post-Inc.

Load Indirect and Pre-Dec.

Load Indirect

Load Indirect and Post-Inc.

Load Indirect and Pre-Dec.

Load Indirect with Displacement

Load Indirect

Load Indirect and Post-Inc.

Load Indirect and Pre-Dec.

Load Indirect with Displacement

Load Direct from SRAM

Store Indirect

Store Indirect and Post-Inc.

Store Indirect and Pre-Dec.

Store Indirect

Store Indirect and Post-Inc.

Store Indirect and Pre-Dec.

Store Indirect with Displacement

Store Indirect

Store Indirect and Post-Inc.

Store Indirect and Pre-Dec.

Store Indirect with Displacement

Store Direct to SRAM

Load Program Memory

In Port

Out Port

Push Register on Stack

Pop Register from Stack

Set Bit in I/O Register

Clear Bit in I/O Register

Logical Shift Left

Logical Shift Right

Rotate Left Through Carry

Rotate Right Through Carry

Arithmetic Shift Right

Swap Nibbles

Flag Set

Flag Clear

Bit Store from Register to T

Bit load from T to Register

Set Carry

Clear Carry

Set Negative Flag

Clear Negative Flag

Set Zero Flag

Clear Zero Flag

Global Interrupt Enable

Global Interrupt Disable

Set Signed Test Flag

Clear Signed Test Flag

Set Twos Complement Overflow.

Clear Twos Complement Overflow

Set T in SREG

Clear T in SREG

Set Half Carry Flag in SREG

Clear Half Carry Flag in SREG

No Operation

Sleep

Watchdog Reset

R0 ← (Z+RAMPZ)

Rd ← Rr

Rd ← K

Rd ← (X)

Rd ← (X), X ← X + 1

X ← X - 1, Rd ← (X)

Rd ← (Y)

Rd ← (Y), Y ← Y + 1

Y ← Y - 1, Rd ← (Y)

Rd ← (Y + q)

Rd ← (Z)

Rd ← (Z), Z ← Z+1

Z ← Z - 1, Rd ← (Z)

Rd ← (Z + q)

Rd ← (k)

(X) ← Rr

(X) ← Rr, X ← X + 1

X ← X - 1, (X) ← Rr

(Y) ← Rr

(Y) ← Rr, Y ← Y + 1

Y ← Y - 1, (Y) ← Rr

(Y + q) ← Rr

(Z) ← Rr

(Z) ← Rr, Z ← Z + 1

Z ← Z - 1, (Z) ← Rr

(Z + q) ← Rr

(k) ← Rr

R0 ← (Z)

Rd ← P

P ← Rr

STACK ← Rr

Rd ← STACK

I/O(P,b) ← 1

I/O(P,b) ← 0

Rd(n+1) ← Rd(n), Rd(0) ← 0

Rd(n) ← Rd(n+1), Rd(7) ← 0

Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7)

Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0)

Rd(n) ← Rd(n+1), n=0..6

Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)

SREG(s) ← 1

SREG(s) ← 0

T ← Rr(b)

Rd(b) ← T

C←1

C←0

N←1

N←0

Z←1

Z←0

I←1

I←0

S←1

S←0

V←1

V←0

T←1

T←0

H←1

H←0

(see specific descr. for Sleep function)

(see specific descr. for WD timer)

8 ATmega603(L) and ATmega103(L)

None

3

None

1

None

1

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

2

None

3

None

1

None

1

None

2

None

2

None

2

None

2

Z,C,N,V

1

Z,C,N,V

1

Z,C,N,V

1

Z,C,N,V

1

Z,C,N,V

1

None

1

SREG(s)

1

SREG(s)

1

T

1

None

1

C

1

C

1

N

1

N

1

Z

1

Z

1

I

1

I

1

S

1

S

1

V

1

V

1

T

1

T

1

H

1

H

1

None

1

None

3

None

1