S5L9284 View Datasheet(PDF) - Samsung

Part Name

Description

Manufacturer

S5L9284 Datasheet PDF : 24 Pages

| |||

S5L9284D

DIGITAL SIGNAL PROCESSOR

PIN DESCRIPTION (Continued)

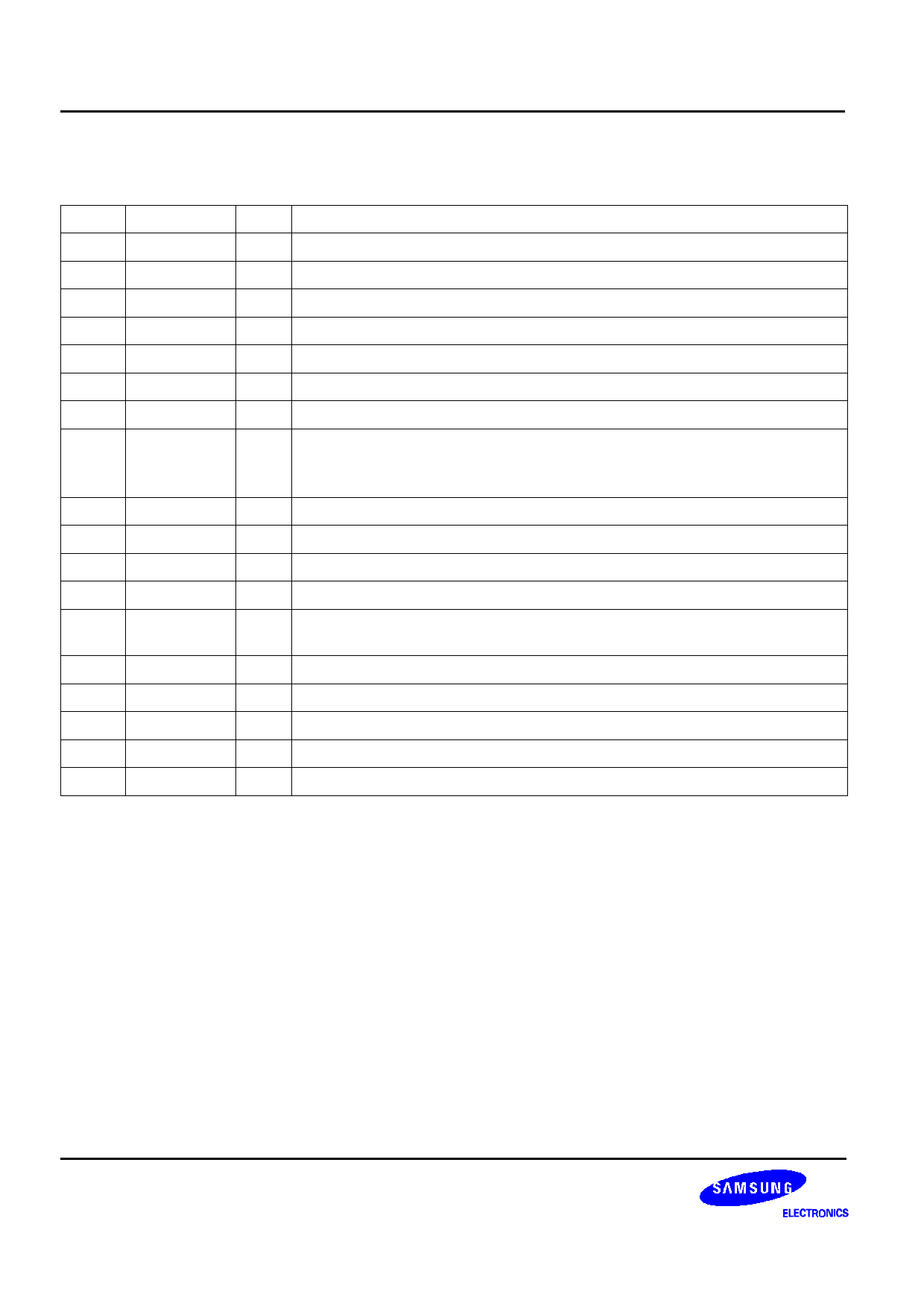

Pin No. Symbol

I/O

Description

63

SEL3

I CD-ROM selection terminal (“L”: CDP, “H”: CD-ROM)

64

SEL4

I SRAM selection terminal (“L”: internal SRAM, “H”: external SRAM)

65

TEST1

I Test terminal (“L”: normal, “H”: test)

66

EFMI

I EFM data input

67

APDO1

O Charge pump output for analog PLL

68

/ISTAT

O The internal status output

69

TRCNT

I Tracking clock input signal

70

LOCK

O Output signal of LKFS conditions sampled PBFR/16

(If LKFS is High, lock is High. If the LKFS is sampled Low at least 8 times by

PBFR/16, lock is Low )

71

PBFR

O Write frame clock (Lock : 7.35kHz)

72

SMEF

O LPF time constant control of the spindle servo error signal

73

SMON

O ON/OFF control signal for spindle servo

74

DVDD2

− Digital supply voltage 2

75

SMDP

O Spindle motor driving output (rough control in the speed mode, phase control in

the phase mode

76

SMSD

O Spindle motor (Velocity control in the phase mode)

77

VCOO

O VCO output

78

VCOI

I VCO inut (when in locked status by means of PBFR, it is 8.6436MHz)

79

DSPEED

I Double speed mode control (“H”: normal speed, “L”: 2-times speed )

80

APDO2

O Analog PLL charge pump output for double speed mode

NOTES:

1. PBFR: 7.35 kHz Write frame clock produced by data which is being reproduced.

2. /PBCK : Channel bit clock of data which being reproduced.

3. /JIT : Display signal of either RAM overflow or underflow for ± 4 frame jitter margin.

6