ST10F271 View Datasheet(PDF) - STMicroelectronics

Part Name

Description

Manufacturer

ST10F271 Datasheet PDF : 173 Pages

| |||

Memory organization

4

Memory organization

ST10F271

The memory space of the ST10F271 is configured in a unified memory architecture. Code

memory, data memory, registers and I/O ports are organized within the same linear address

space of 16M Bytes. The entire memory space can be accessed Byte wise or Word wise.

Particular portions of the on-chip memory have additionally been made directly bit

addressable.

IFLASH: 128K Bytes of on-chip Flash memory. It is divided in 6 blocks (B0F0...B0F5) that

constitute the Bank 0. When Bootstrap mode is selected, the Test-Flash Block B0TF

(8Kbyte) appears at address 00’0000h: refer to Chapter 5: Internal Flash memory on

page 24 for more details on memory mapping in boot mode. The summary of address range

for IFlash is the following:

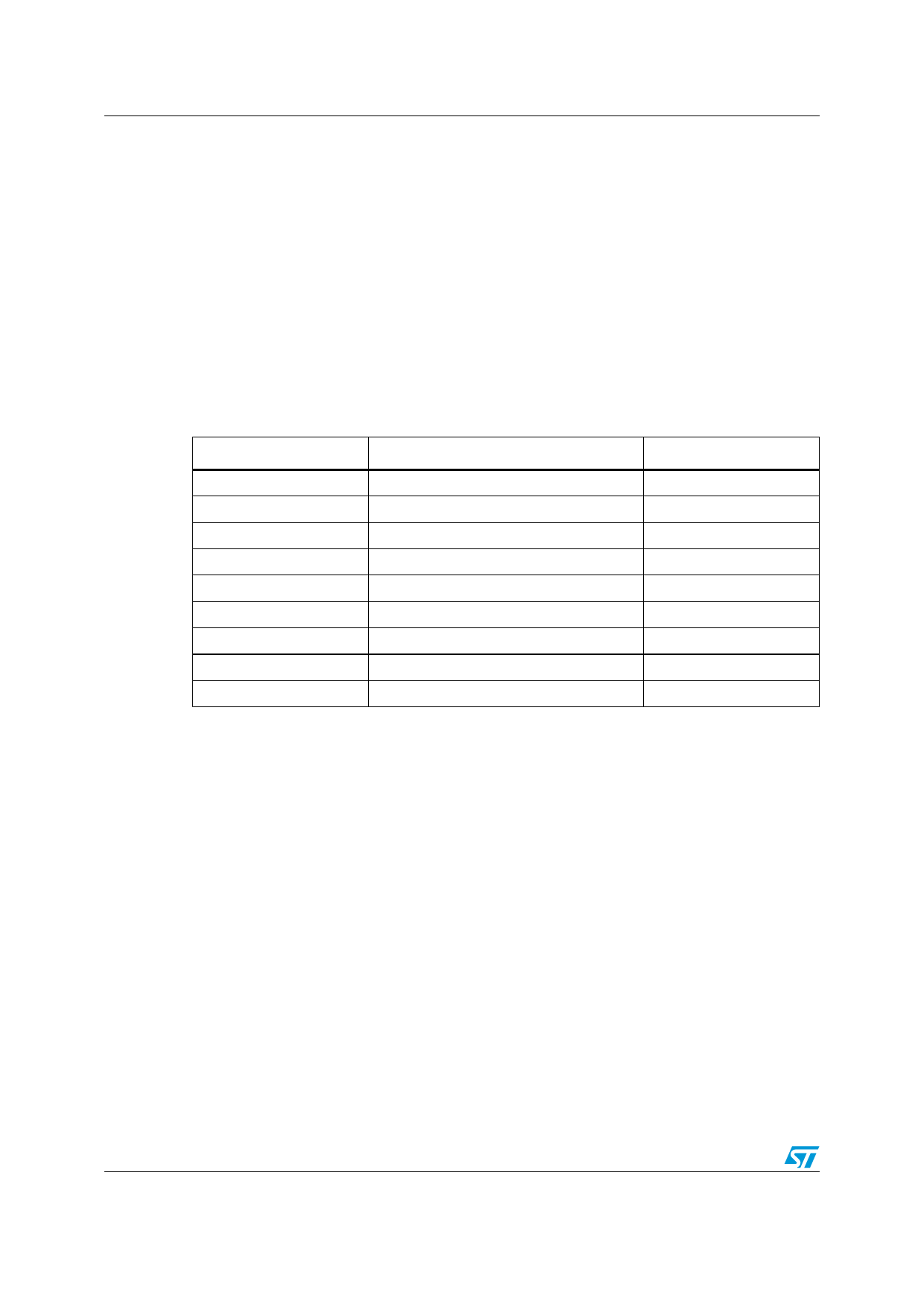

Table 2. Summary of IFLASH address range

Blocks

User Mode

Size

B0TF

Not visible

8K

B0F0

00’0000h - 00’1FFFh

8K

B0F1

00’2000h - 00’3FFFh

8K

B0F2

00’4000h - 00’5FFFh

8K

B0F3

00’6000h - 00’7FFFh

8K

B0F4

01’8000h - 01’FFFFh

32K

B0F5

02’0000h - 02’FFFFh

64K

Reserved (1)

03’0000h - 03’FFFFh / RESERVED

64K

Reserved (1)

04’0000h - 04’FFFFh / RESERVED

64K

(1) This area must be reserved by the application mapping.

IRAM: 2K Bytes of on-chip internal RAM (dual-port) is provided as a storage for data,

system stack, general purpose register banks and code. A register bank is 16 Wordwide (R0

to R15) and / or Bytewide (RL0, RH0, …, RL7, RH7) general purpose registers group.

XRAM: 8K+2K Bytes of on-chip extension RAM (single port XRAM) is provided as a storage

for data, user stack and code.

The XRAM is divided into 2 areas, the first 2K Bytes named XRAM1 and the second 8K

Bytes named XRAM2, connected to the internal XBUS and are accessed like an external

memory in 16-bit demultiplexed bus-mode without wait state or read/write delay (31.25ns

access at 64MHz CPU clock). Byte and Word accesses are allowed.

The XRAM1 address range is 00’E000h - 00’E7FFh if XPEN (bit 2 of SYSCON register),

and XRAM1EN (bit 2 of XPERCON register) are set. If XRAM1EN or XPEN is cleared, then

any access in the address range 00’E000h - 00’E7FFh will be directed to external memory

interface, using the BUSCONx register corresponding to address matching ADDRSELx

register.

The XRAM2 address range is the one selected programming XADRS3 register, if XPEN (bit

2 of SYSCON register), and XRAM2EN (bit 3 of XPERCON register) are set. If bit XPEN is

cleared, then any access in the address range programmed for XRAM2 will be directed to

20/173