TDA8760K View Datasheet(PDF) - Philips Electronics

Part Name

Description

Manufacturer

TDA8760K Datasheet PDF : 28 Pages

| |||

Philips Semiconductors

10-bit high-speed analog-to-digital

converter

Product specification

TDA8760

Notes

1. The circuit has two clock inputs: CLK and CLK. There are three modes of operation:

a) TTL mode 1:

CLK input is at TTL level with a threshold voltage of 1.5 V and sampling is taken on the falling edge of the clock

input signal. CLK decoupled to DGND via a 100 nF capacitor.

b) TTL mode 2:

CLK input is at TTL level with threshold voltage of 1.5 V and sampling is taken on the rising edge of the clock

input signal. CLK decoupled to DGND via a 100 nF capacitor.

c) TTL mode 3:

CLK and CLK inputs are at differential TTL levels.

d) AC driving modes:

When driving the CLK input directly and with any AC signal of minimum 0.5 V (p-p) and with a DC level of 1.5 V,

the sampling takes place at the falling edge of the clock signal.

When driving the CLK input with the same signal, sampling takes place at the rising edge of the clock signal.It is

recommended to decouple the CLK or CLK input to DGND via a 100 nF capacitor.

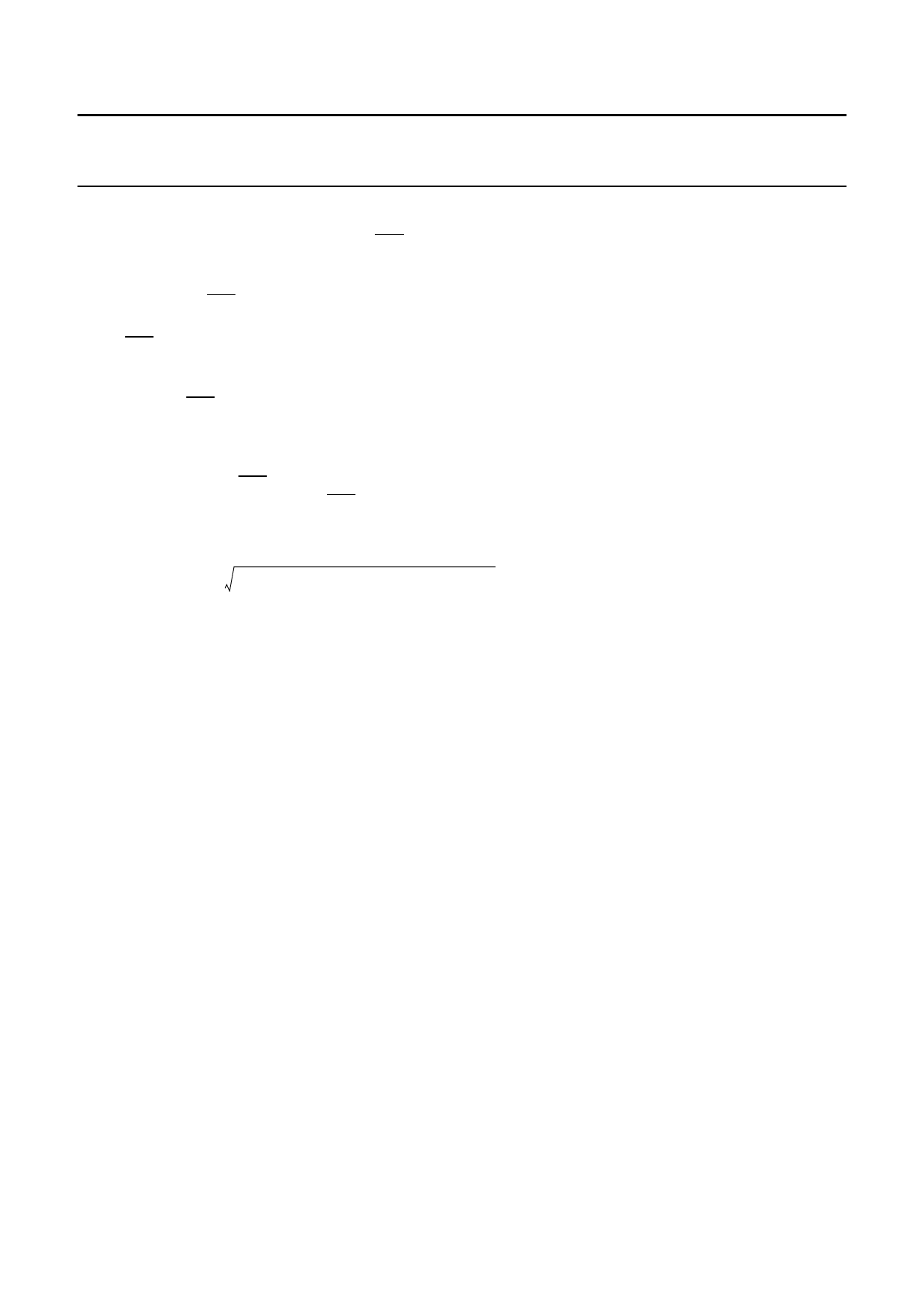

2. THD (total harmonic distortion) is obtained with the addition of the first five harmonics:

a) THD = 20 log-------------------------------------------------------F--------------------------------------------------------

(2nd)2 + (3rd)2 + (4th)2 + (5th)2 + (6th)2

b) F being the fundamental harmonic referenced at 0 dB for a full-scale sine wave input.

3. AC linearity: full-scale differential sine wave (fi = 4.43 MHz; fclk = 40 MHz).

4. Effective bits with differential input and single input are respectively executed with full scale differential input and

full-scale single sine wave.

5. Effective bits are obtained via a Fast Fourier Transformer (FFT) treatment taking 8K acquisition points per period.

The calculation takes into account all harmonics and noise up to half of the clock frequency (NYQUIST frequency).

Conversion to SNR: SNR = EB × 6.02 + 1.76 dB.

6. Output data acquisition: the output data is available after the maximum delay of td.

7. tCPH of 9 ns (minimum) can be applied at the penalty of 0.5 effective bit drop compared to typical values.

8. Intermodulation measured relative to either tone with analog input frequencies of 4.43 MHz and 4.53 MHz. The two

input signals have the same amplitude and the total amplitude of both signals provides full-scale to the converter.

9. The −3 dB (or −1 dB) analog bandwidth is determined by the 3 dB (or 1 dB) reduction in the reconstructed output,

the input being a full-scale sine wave.

1996 Sep 12

13