CDP1805AC View Datasheet(PDF) - Intersil

Part Name

Description

Manufacturer

CDP1805AC Datasheet PDF : 30 Pages

| |||

CDP1805AC, CDP1806AC

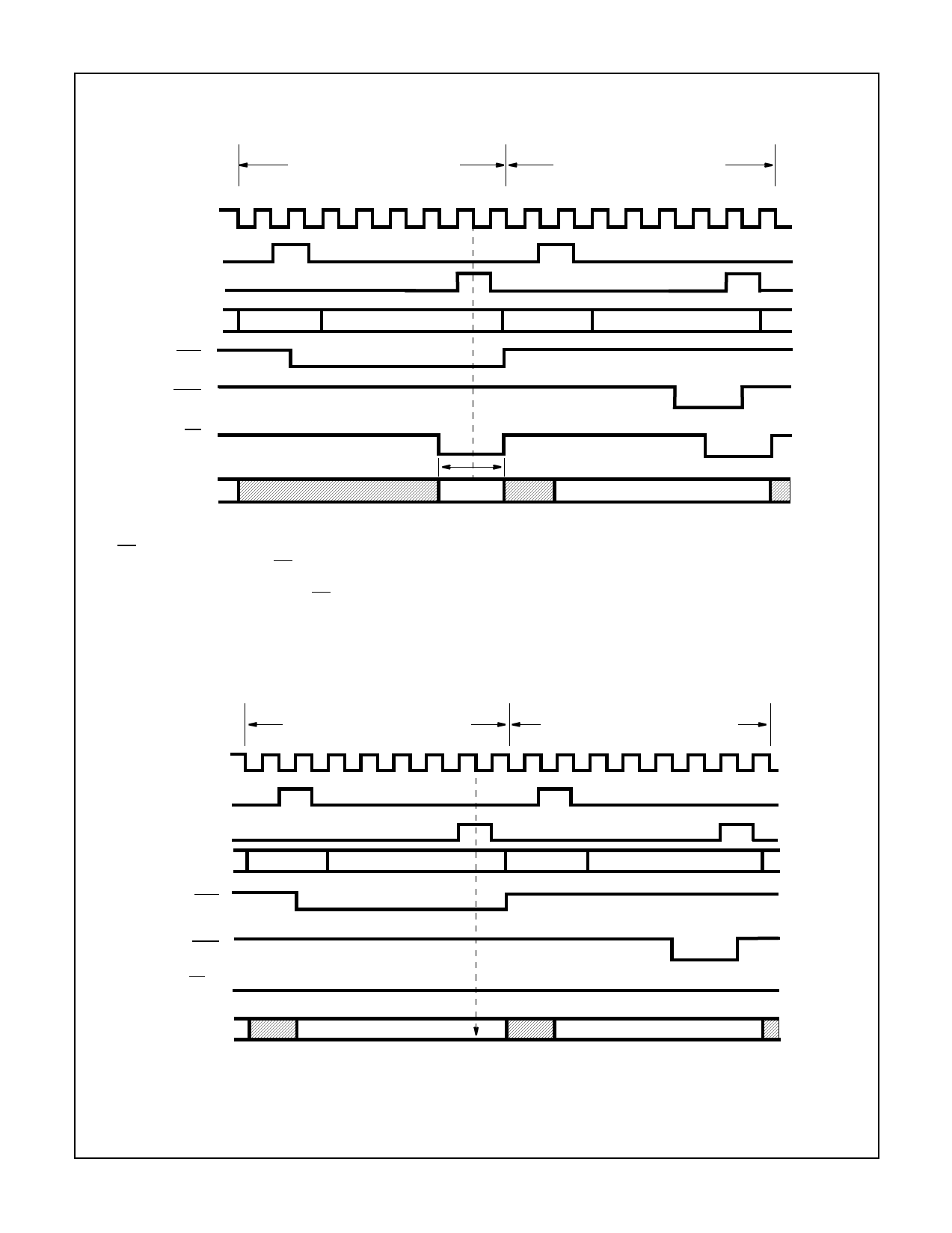

Timing Waveforms For Possible Operating Modes

INTERNAL RAM READ CYCLE

INTERNAL RAM WRITE CYCLE

CLOCK

TPA

TPB

MEMORY

ADDRESS

MRD

00 10 20 30 40 50 60 70 00 10 20 30 40 50 60 70

01 11 21 31 41 51 61 71 01 11 21 31 41 51 61 71

HIGH BYTE

LOW BYTE

HIGH BYTE

LOW BYTE

MWR

†ME

IN

DATA

BUS

VALID DATA FROM MEMORY

VALID DATA FROM CPU

NOTE:

8. ME has a minimum setup and hold time with respect to the beginning of clock 70. For a memory read operation, RAM data will appear on

the data bus during the time ME is active after clock 31. The time shown can be longer, if for instance, a DMA out operation is performed

on internal RAM data, to allow data enough time to be latched into an external device. The internal RAM is automatically deselected at

the end of clock 71 independent of ME.

† For CDP1805AC only.

FIGURE 3. INTERNAL MEMORY OPERATION TIMING WAVEFORMS

CLOCK

TPA

TPB

MEMORY

ADDRESS

EXTERNAL MEMORY READ CYCLE

EXTERNAL MEMORY WRITE CYCLE

00 10 20 30 40 50 60 70 00 10 20 30 40 50 60 70

01 11 21 31 41 51 61 71 01 11 21 31 41 51 61 71

HIGH BYTE

LOW BYTE

HIGH BYTE

LOW BYTE

MRD

MWR

†ME IN

(HIGH)

DATA

BUS

DATA LATCHED IN CPU

VALID DATA FROM CPU

NOTE:

† For CDP1805AC only.

FIGURE 4. EXTERNAL MEMORY OPERATION TIMING WAVEFORMS

7