CDP1805AC View Datasheet(PDF) - Intersil

Part Name

Description

Manufacturer

CDP1805AC Datasheet PDF : 30 Pages

| |||

CDP1805AC, CDP1806AC

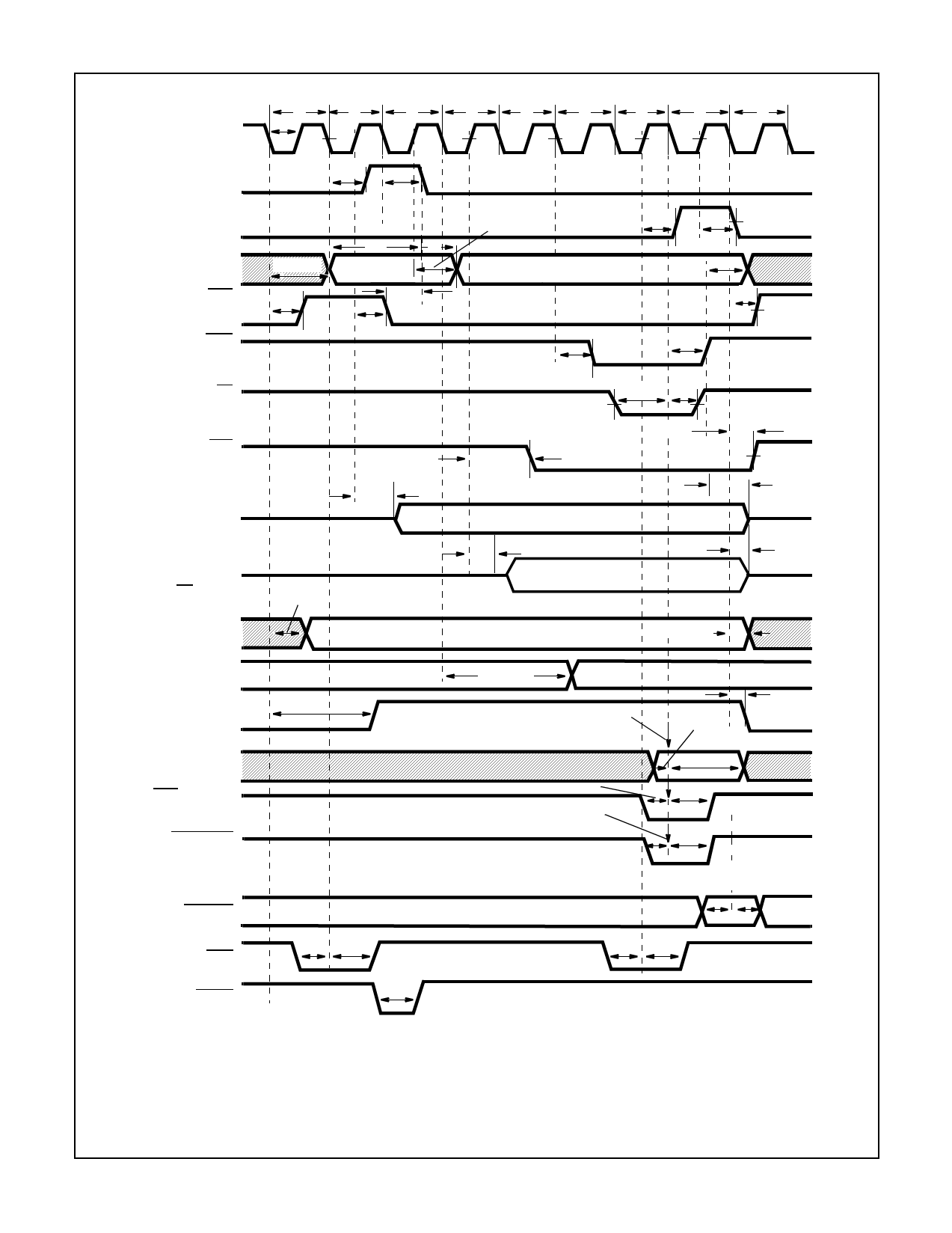

CLOCK

TPA

TPB

MEMORY

ADDRESS

MRD

(MEMORY

READ CYCLE)

MWR

(MEMORY

WRITE CYCLE)

† ME

(MEMORY

ENABLE)

†† EMS

(EXTERNAL

MEMORY

SELECT)

DATA FROM

CPU TO BUS

DATA FROM

INTERNAL MEMORY

TO BUS (ME = LOW)

STATE CODES

0

tW

00 01

1

10 11

2

20 21

3

4

5

30 31 40 41 50 51

6

7

60 61 70 71

0

00 01

tPLH

tPHL

tSU

tH

tPLH, tPHL

HIGH ORDER

ADDRESS BYTE

tPLH

tSU

tPHL

tPLH,

tPHL

tPLH, tPHL

LOW ORDER

ADDRESS BYTE

tPLH

tPHL

tH

tPHL

tPHL

tPLH

tSU IS ALLOWABLE

INTERNAL RAM

ACCESS TIME

tSU

tH

tPLH

tPHL

tH

tPLH,

tPHL

tPLH

tPHL

tPLH, tPLH

tPLH, tPHL

Q

N0, N1, N2

(I/O EXECUTION

CYCLE)

tPLH

tPLH, tPHL

DATA LATCHED

IN CPU

tPHL

tSU

DATA FROM

BUS TO CPU

DMA REQUEST

INTERRUPT

REQUEST

DMA SAMPLED (S1, S2, S3)

INTERRUPT

SAMPLED (S1, S2)

tH

tSU tH

tSU tH

FLAG LINES

SAMPLED END OF S0

EF1 - EF4

WAIT

CLEAR

tSU tH

tWL

tSU tH

tSU tH

NOTES:

† This Timing Diagram is used to show signal relationships only, and does not represent any specific machine cycle.

† All measurements are referenced to 50% point of the wave forms.

† Shaded areas indicate “don’t care” or undefined state. Multiple transitions may occur during this period.

† For the run (RAM only) mode only.

†† For the run (RAM/ROM) mode only.

FIGURE 5. TIMING WAVEFORMS

8