MC1377P View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MC1377P Datasheet PDF : 18 Pages

| |||

MC1377

Timing Circuitry

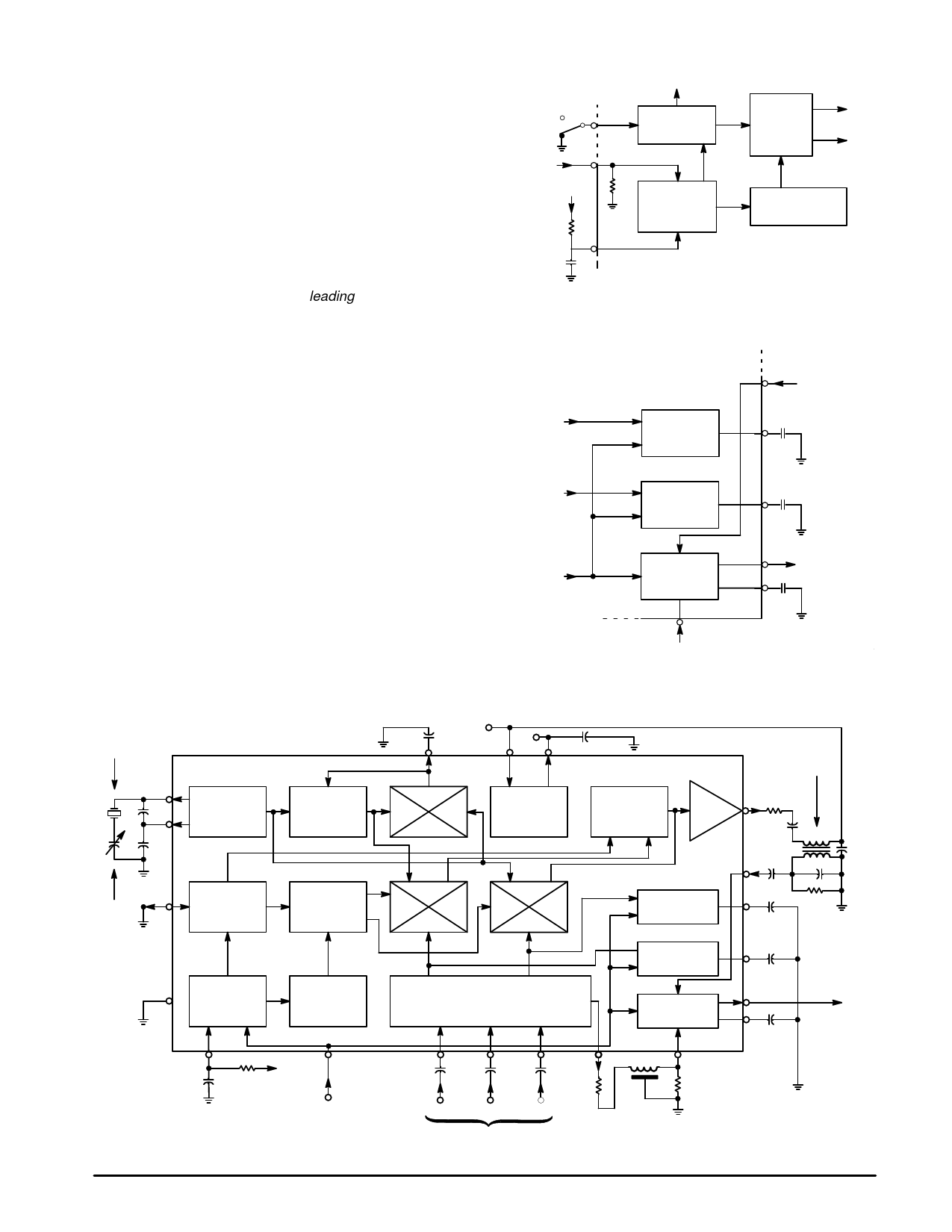

The composite sync input at Pin 2 performs three

important functions: it provides the timing (but not the

amplitude) for the sync in the final output; it drives the black

level clamps in the modulators and output amplifier; and it

triggers the ramp generator at Pin 1, which produces burst

envelope and PAL switching. A representative block diagram

of the timing circuitry is shown in Figure 5.

In order to produce a color burst, a burst envelope must be

generated which “gates” a color subcarrier into the R–Y and

B–Y modulators. This is done with the ramp generator at

Pin 1.

The ramp generator at Pin 1 is an R–C type in which the

pin is held low until the arrival of the leading edge of sync. The

rising ramp function, with time constant R–C, passes through

two level sensors – the first one starts the gating pulse and

the second stops it (see Figure 10). Since the “early” part of

the exponential is used, the timing provided is relatively

accurate from chip–to–chip and assembly–to–assembly.

Fixed components are usually adequate. The ramp

continues to rise for more than half of the line interval, thereby

inhibiting burst generation on “half interval” pulses on vertical

front and back porches. The ramp method will produce burst

on the vertical front and back “porches” at full line intervals.

R–Y, B–Y Clamps and Output Clamp/Amplifier

The sync signal, shown in the block diagram of Figure 6,

drives the R–Y and B–Y clamps which clamp the R–Y and

B–Y signals to reference black during the blanking periods.

The output amplifier/clamp provides this same function plus

combines and amplifies the chroma and luma components

for composite video output.

Application Circuit

Figure 7 illustrates the block diagram of the MC1377 and

the external circuitry required for typical operation.

Figure 5. Timing Circuitry

PAL/

NTSC 20

Sync

Input

2

VB

R

H/2

PAL/NTSC

Control

Line Drive

10k Latching

Ramp

Generator

Burst

Pulse

Driver

Burst Flag

Dual

Comparator

C1

Figure 6. R–Y, B–Y and Output Amplifier Clamps

Chroma

10

B–Y

B–Y

11

Clamp

0.1

R–Y

R–Y

12

Clamp

0.1

9 Composite

Sync

Output

Amp/Clamp

Video

7

0.01

8

–Y

Figure 7. Block Diagram and Application Circuit

3.58/

4.43*

0.01VCC

VB

MHz

19

14

16 0.1

TOKO 166NNF

–10264AG

17

220

18

220

20

5.0 to

25pF

NTSC/

PAL Select

15

Osc/

Buffer

H/2

PAL/NTS

C

Control

Latching

Ramp

Gen

Voltage

Controlled

90°

Burst

Pulse

Driver

Dual

Comparator

1

56k

0.001

mica

* Refers to the choice NTSC/PAL

* (3.58 MHz/4.43 MHz).

2

VB

Composite

Sync

Input

8.2V

Regulator

90°

R–Y

0°

B–Y

R–Y

B–Y

Color Difference and

Luminance Matrix

–Y

3+ 4 + 5 + 6

15µF 15µF 15µF

1.0k

R

G

B

R, G, B Inputs

PAL

Switch

0/180°

Chroma

Amp

13 220

100/

62*

B–Y

Clamp

10

11 1000

0.1

R–Y

Clamp

Output Amp/

Clamp

–Y

8

1.0k

400ns

Y Delay

12

0.1

9

7 0.01

0.1

47/33*

3.3k

Composite

Video Output

MOTOROLA ANALOG IC DEVICE DATA

5