UPD160062 View Datasheet(PDF) - NEC => Renesas Technology

Part Name

Description

Manufacturer

UPD160062 Datasheet PDF : 18 Pages

| |||

µ PD160062

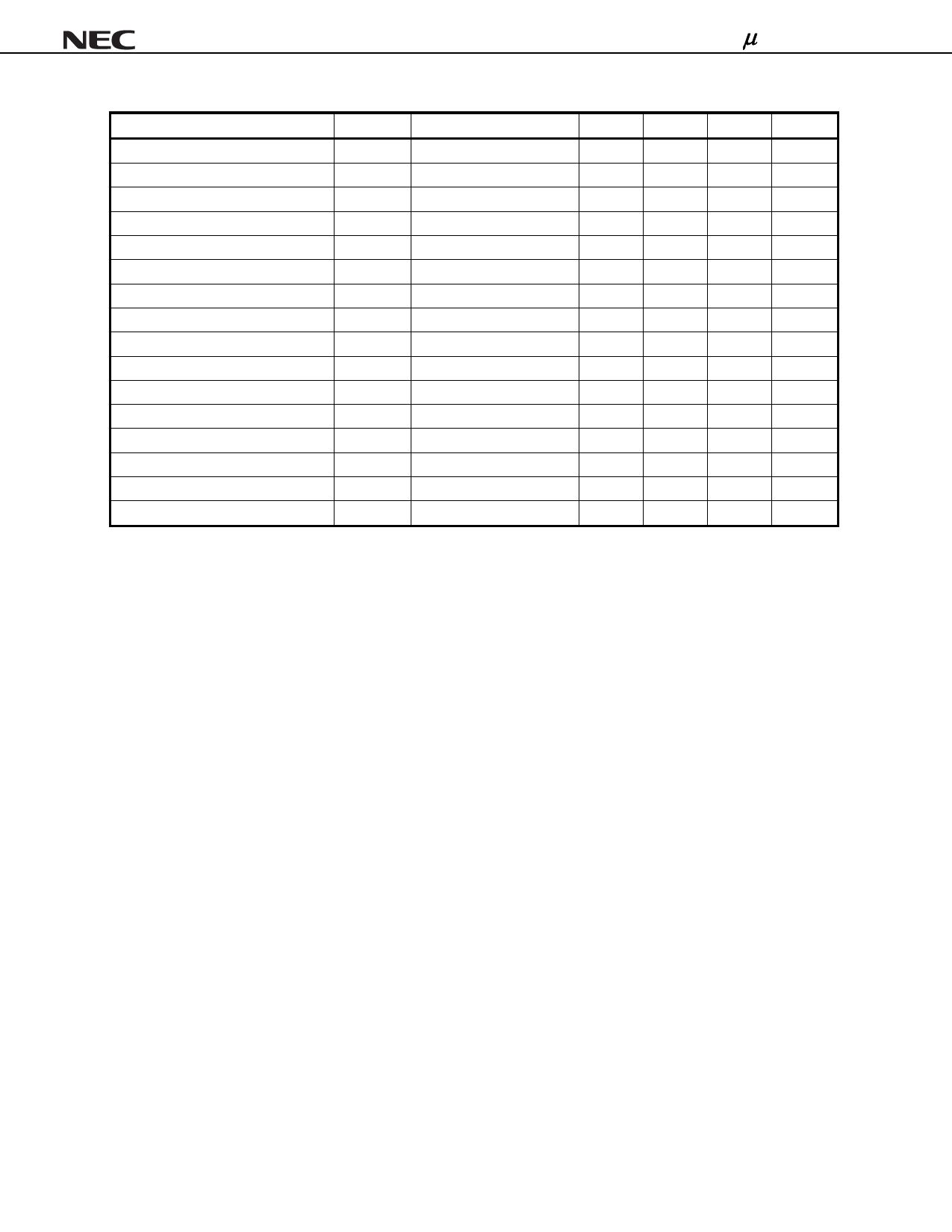

Timing Requirement (TA = −10 to +75°C, VDD1 = 2.3 to 3.6 V, VSS1 = 0 V, tr = tf = 5.0 ns)

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Clock Pulse Width

PWCLK

22

Clock Pulse High Period

PWCLK(H)

4

Clock Pulse Low Period

PWCLK(L)

4

Data Setup Time

tSETUP1

4

Data Hold Time

tHOLD1

0

Start Pulse Setup Time

tSETUP2

4

Start Pulse Hold Time

tHOLD2

0

POL21, POL22 Setup Time

tSETUP3

4

POL21, POL22 Hold Time

tHOLD3

0

STB Pulse Width

PWSTB

2

Last Data Timing

tLDT

2

CLK-STB Time

tCLK-STB

CLK ↑ → STB ↑

6

STB-CLK Time

tSTB-CLK

STB ↑ → CLK ↑

9

Time Between STB and Start Pulse tSTB-STH

STB ↑ → STHR(STHL) ↑

2

POL-STB Time

tPOL-STB

POL ↑ or ↓ → STB ↑

–5

STB-POL Time

tSTB-POL

STB ↓ → POL ↓ or ↑

6

Remark Unless otherwise specified, the input level is defined to be VIH = 0.7 VDD1, VIL = 0.3 VDD1.

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

CLK

CLK

ns

ns

CLK

ns

ns

Data Sheet S16449EJ1V0DS

15