UPD75304BGC View Datasheet(PDF) - NEC => Renesas Technology

Part Name

Description

Manufacturer

UPD75304BGC Datasheet PDF : 76 Pages

| |||

µPD75304B,75306B,75308B

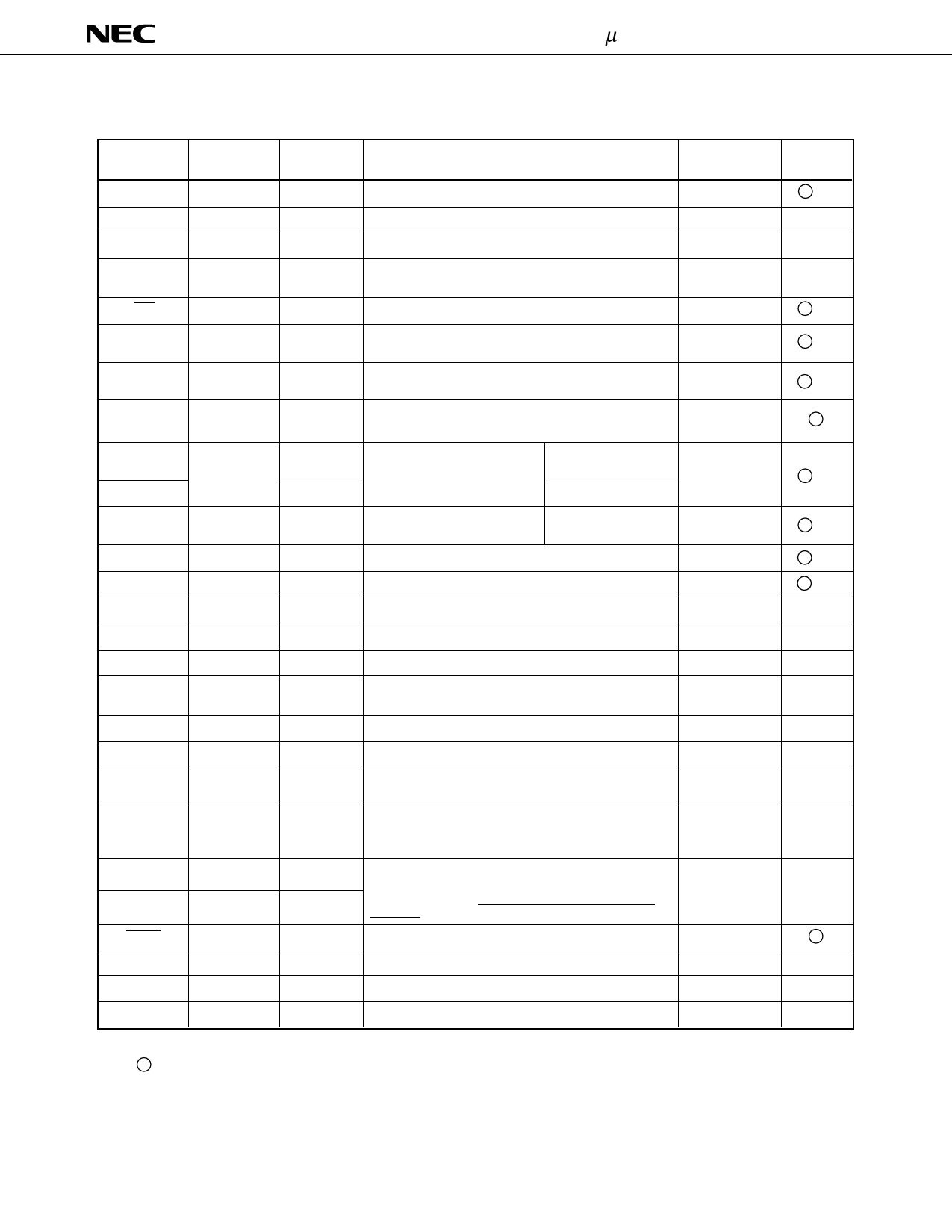

3.2 NON-PORT PINS

Pin Name

TI0

PTO0

PCL

BUZ

SCK

SO/SB0

Input/Output

Input

Input/output

Input/output

Input/output

Input/output

Input/output

SI/SB1

Input/output

INT4

Input

INT0

INT1

Input

INT2

Input

KR0 to KR3 Input/output

KR4 to KR7 Input/output

S0 to S23

Output

S24 to S31

Output

COM0 to COM3

Output

VLC0 to VLC2

—

BIAS

LCDCL *4

Output

Input/output

SYNC *4

Input/output

X1, X2

Input

XT1

XT2

RESET

NC *5

VDD

VSS

Input

—

Input

—

—

—

Dual-

Function Pin

Function

P13

External event pulse input pin to timer/event counter

P20

Timer/event counter output pin

P22

Clock output pin

Fixed frequency output pin (for buzzer or system clock

P23

trimming)

P01

Serial clock input/output pin

Serial data output pin

P02

Serial bus input/output pin

P03

Serial data input pin

Serial bus input/output pin

P00

Edge detection vectored interrupt input pin (both rising

edge and falling edge detection effective)

P10

Edge detection vectored

interrupt input pin (detection

Clock synchronous

system

edge selectable)

P11

Asynchronous

P12

Edge detection testable input

pin (rising edge detection)

Asynchronous

P60 to P63 Parallel falling edge detection testable input pin

P70 to P73 Parallel falling edge detection testable input pin

—

Segment signal output pin

BP0 to BP7 Segment signal output pin

—

Common signal output pin

—

LCD drive power supply pin

On-chip split resistor (mask option)

—

External split resistor cut output pin

P30

External expansion driver drive clock output pin

P31

External expansion driver synchronization clock output

pin

Main system clock oscillation crystal/ceramic connection

—

pin. For external clock, the external clock signal is input

to X1 and its opposite phase is input to X2.

—

Subsystem clock oscillation crystal connection pin. For

external clock, the external clock signal is input to XT1

and XT2 is opened. XT1 can be used as a 1-bit input

—

(test) pin.

—

System reset input pin

—

NO CONNECTION

—

Positive power supply pin

—

GND potential pin

After

Reset

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

Input

*2

*2

*2

—

*3

Input

Input

—

—

—

—

—

—

* 1. : Schmitt trigger input

2. Display outputs are selected with VLCX shown below as the input source.

S0 to S31: VLC1, COM0 to COM2: VLC2, COM3: VLC0

However, the level of each display output depends on the display output and VLCX external circuit.

I/O Circuit

Type *1

B -C

E-B

E-B

E-B

F -A

F -B

M -C

B

B -C

B -C

F -A

F -A

G-A

G-C

G-B

—

—

E-B

E-B

—

—

B

—

—

—

11