UPD75P0076GT View Datasheet(PDF) - NEC => Renesas Technology

Part Name

Description

Manufacturer

UPD75P0076GT Datasheet PDF : 62 Pages

| |||

µPD75P0076

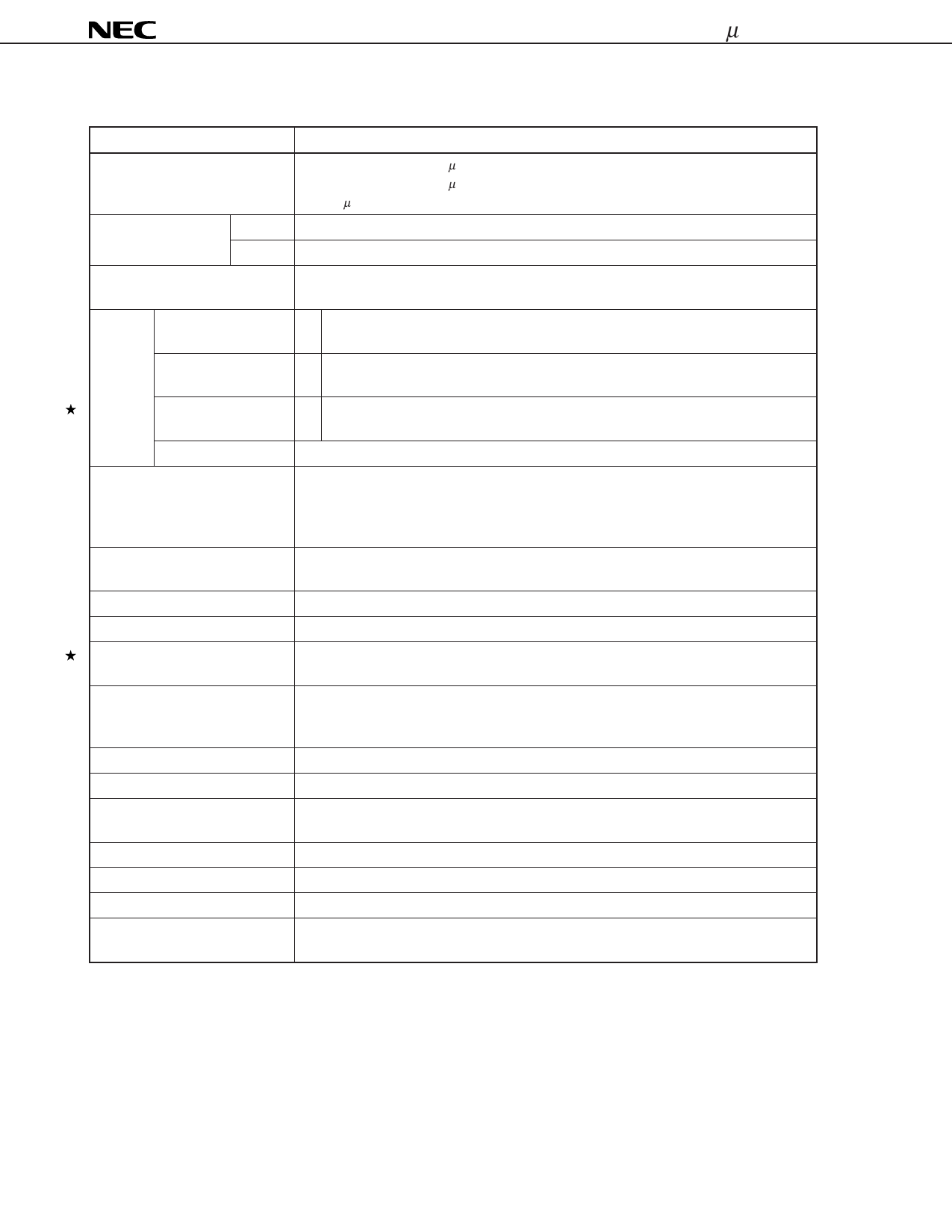

Functional Outline

Parameter

Instruction execution time

On-chip memory

PROM

RAM

General-purpose register

Input/

output

port

CMOS input

CMOS input/output

Timer

N-ch open-drain

input/output pins

Total

Serial interface

A/D converter

Bit sequential buffer

Clock output (PCL)

Buzzer output (BUZ)

Vectored interrupts

Test input

System clock oscillator

Standby function

Operating ambient temperature

Power supply voltage

Package

Function

• 0.95, 1.91, 3.81, 15.3 µs (@ 4.19 MHz with main system clock)

• 0.67, 1.33, 2.67, 10.7 µs (@ 6.0 MHz with main system clock)

• 122 µs (@ 32.768 kHz with subsystem clock)

16384 x 8 bits

512 x 4 bits

• 4-bit operation: 8 x 4 banks

• 8-bit operation: 4 x 4 banks

12 Connections of on-chip pull-up resistors can be specified by software: 7

Also used for analog input pins: 4

12 Connections of on-chip pull-up resistors can be specified by software: 12

Also used for analog input pins: 4

8 13-V withstand voltage

32

4 channels

• 8-bit timer/event counter: 2 channels (can be used as the 16-bit timer/event counter)

• 8-bit basic interval timer/watchdog timer: 1 channel

• Watch timer: 1 channel

• 3-wire serial I/O mode ··· MSB or LSB can be selected for transferring first bit

• 2-wire serial I/O mode

8-bit resolution x 8 channels (1.8 V ≤ AVREF ≤ VDD)

16 bits

• Φ, 1.05 MHz, 262 kHz, 65.5 kHz (@ 4.19 MHz with main system clock)

• Φ, 1.5 MHz, 375 kHz, 93.8 kHz (@ 6.0 MHz with main system clock)

• 2, 4, 32 kHz (@ 4.19 MHz with main system clock or

@ 32.768 kHz with subsystem clock)

• 2.93, 5.86, 46.9 kHz (@ 6.0 MHz with main system clock)

External: 3, Internal: 4

External: 1, Internal: 1

• Ceramic or crystal oscillator for main system clock oscillation

• Crystal oscillator for subsystem clock oscillation

STOP/HALT mode

TA = –40 to +85 ˚C

VDD = 1.8 to 5.5 V

• 42-pin plastic shrink DIP (600 mil, 1.778-mm pitch)

• 42-pin plastic shrink SOP (375 mil, 0.8-mm pitch)

2