XR-T56L22AD View Datasheet(PDF) - Exar Corporation

Part Name

Description

Manufacturer

XR-T56L22AD Datasheet PDF : 16 Pages

| |||

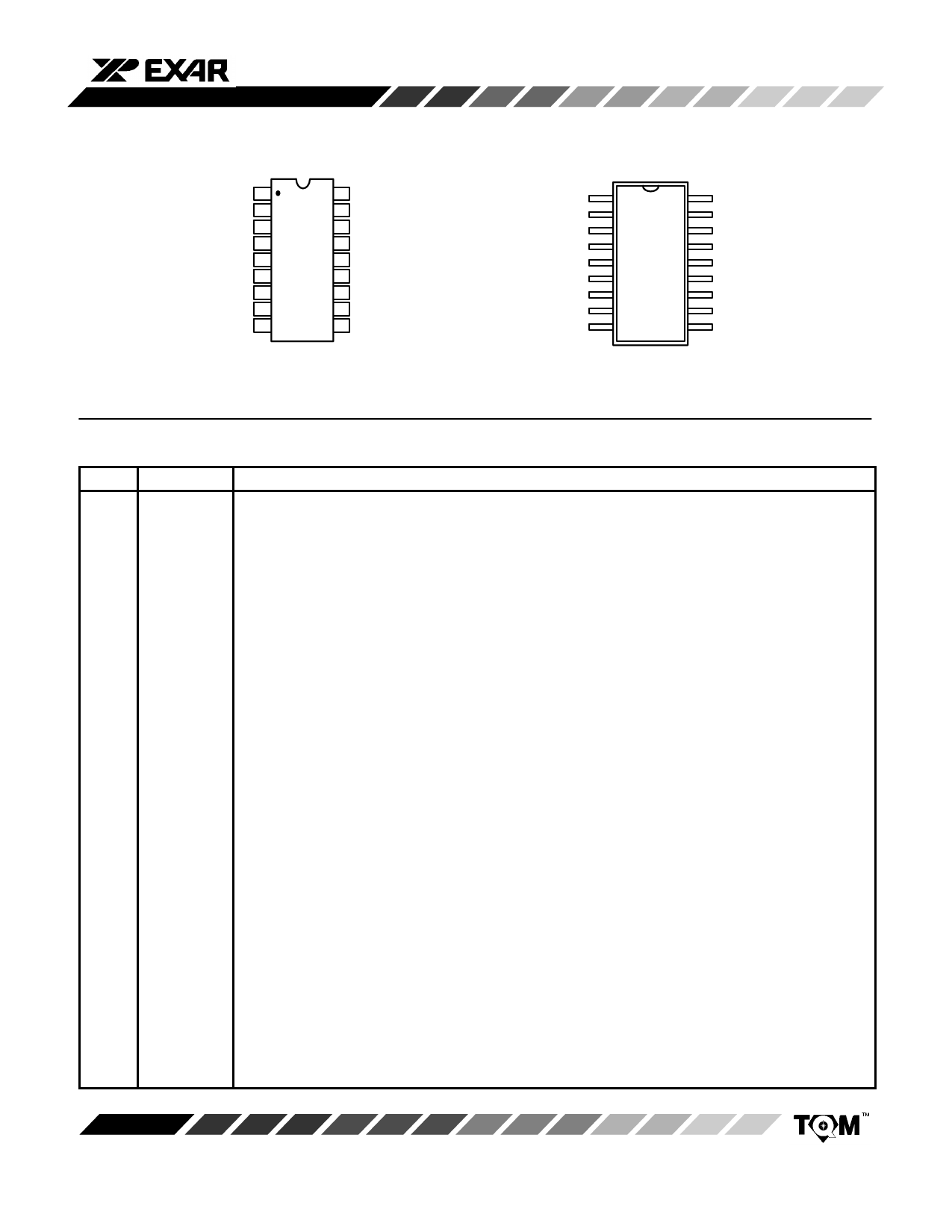

PIN CONFIGURATION

ANA GND 1

ALBO1 2

ALBO2 3

AMP-I/P 4

AMP +I/P 5

AMP -O/P 6

AMP +O/P 7

DIG GND 8

DATA+ 9

18 ALBO FIL

17 LC BIAS

16 LC I/P

15 PHASE CONT.

14 REG CONT.

13 VREF

12 VCC

11 CLOCK O/P

10 DATA-

18 Lead PDIP, CDIP (0.300”)

XR-T56L22

ANA GND

ALBO1

ALBO2

AMP-I/P

AMP +I/P

AMP -O/P

AMP +O/P

DIG GND

DATA+

1

18

2

17

3

16

4

15

5

14

6

13

7

12

8

11

9

10

ALBO FIL

LC BIAS

LC I/P

PHASE CONT.

REG CONT.

VREF

VCC

CLOCK O/P

DATA-

18 Lead SOIC (Jedec, 0.300”)

PIN DESCRIPTION

Pin # Symbol

1

ANA GND

2

ALBO 1

3

ALBO 2

4

AMP - I/P

5

AMP + I/P

6

AMP - O/P

7

AMP + O/P

8

DIG GND

9

DATA+

10

DATA-

11 CLOCK O/P

12

VCC

13

VREF

14 REG CONT

15

PHASE

CONT

16

LC I/P

17

LC BIAS

18

ALBO FIL

Description

Ground for Analog Sections of IC and Substrate.

ALBO PORT 1 Output. Port impedance varies between 25W and 20kW proportional to input signal

level.

ALBO PORT 2 Output. Similar to pin 2.

Inverting Input of Signal Preamp RIN > 20kW.

Non-Inverting Input of Signal Preamp. RIN > 20kW.

Inverting Output of Signal Pre-amp. Rout < 200W. DC level typically 3.2V.

Non-inverting Output of Signal Pre-amp. Similar to pin 6.

Ground for Digital Portion of IC.

Positive Data Driver Output (Open Collector). VOL < 0.95V @ lOUT = 32mA.

Negative Data Driver Output (Open Collector). VOL < 0.95V @ lOUT = 32mA.

Phase Shifted Clock Output (Open Collector). Decouple to GND with 0.1mF if not required. With

Rpull-up = 1K, VOL < 1.1V @ IOUT = 4mA.

Input Pin of Shunt Regulator and Supply Pin for IC. For voltage feed applications the regulator

must be disabled and a 5V + 5% supply connected. For line feed a current of 48-120mA is required.

ICC < 8.75mA @ RON, ALBO = 25W typical.

Output Voltage of Internal Reference of Shunt Regulator. For parallel operation of regulators

should be tied to pin 13 of 2nd T56L22 device. VREF approxi-mately VCC/2. Decouple to GND with

0.1mF.

Input Voltage of Shunt Regulator Amp. To inhibit regulator, pin should be tied to ground. For line

feed operation decouple to GND with 0.1mF. For parallel operation of regulators tie pin 14 of 2nd

T56L22 device. VREG approximately VREF.

Phase Shift Adjust Input. A resistor to GND from the pin allows adjustment of phase shift from 905

to approximately 05. RP typical 1.8K to 1K. Vphase typical 340mV.

Clock Amplifier Input. Pulsed with current from clock comparator. Connect LC tank between 16, 17

for clock recovery. Ickon = —110mA typical.

Clock Amplifier Reference Voltage. VLC = 3.6V typical.

Control Pin for ALBO Ports. Voltage developed across a capacitor on this pin defines ALBO on

impedance VALBO = 1.5V typical.

Rev. 1.02

3