Z89C00 View Datasheet(PDF) - Zilog

Part Name

Description

Manufacturer

Z89C00 Datasheet PDF : 28 Pages

| |||

ZILOG

PRELIMINARY

Z89C00

16-BIT DIGITAL SIGNAL PROCESSOR

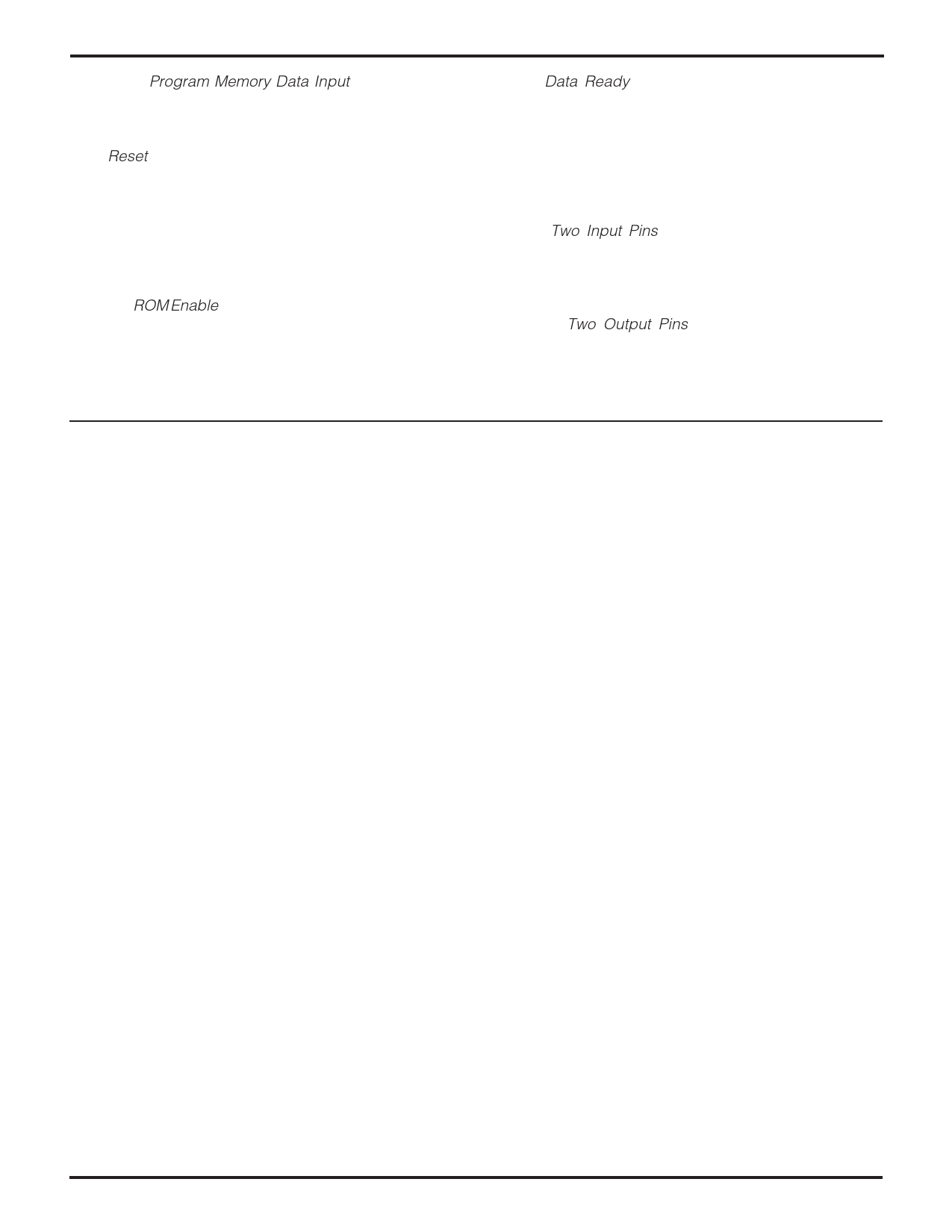

PD15-PD0 Program Memory Data Input (input). Instruc-

tions or data are read from the address specified by PD15-

PD0, through these pins and are executed or stored.

/RES Reset (input, active Low). Asynchronous reset signal.

A Low level on this pin generates an internal reset signal.

The /RES signal must be kept Low for at least one clock

cycle. The CPU pushes the contents of the PC onto the

stack and then fetches a new Program Counter (PC) value

from program memory address 0FFCH after the Reset

signal is released. RES Low tri-states the PA and PD bases.

/ROMEN ROM Enable (input). An active Low signal enables

the internal ROM. Program execution begins at 0000H

from the ROM. An active High input disables the ROM and

external fetches occur from address 0000H.

/RDYE Data Ready (input). User-supplied Data Ready

signal for data to and from external data bus. This pin

stretches the /EI and ER//W lines and maintains data on the

address bus and data bus. The ready signal is sampled

from the rising edge of the clock with appropriate setup

and hold times. The normal write cycle will continue from

the next rising clock only if ready is active.

UI1-UI0 Two Input Pins (input). General purpose input

pins. These input pins are directly tested by the conditional

branch instructions. These are asynchronous input signals

that have no special clock synchronization requirements.

UO1-UO0 Two Output Pins (output). General purpose

output pins. These pins reflect the inverted value of status

register bits S5 and S6. These bits may be used to output

data by writing to the status register.

ADDRESS SPACE

Program Memory. Programs of up to 4K words can be

masked into internal ROM. Four locations are dedicated to

the vector address for the three interrupts (0FFDH-0FFFH)

and the starting address following a Reset (0FFCH). Internal

ROM is mapped from 0000H to 0FFFH, and the highest

location for program is 0FFBH. If the /ROMEN pin is held

High, the internal ROM is inactive and the processor

executes external fetches from 0000H to FFFFH. In this

case, locations FFFC-FFFF are used for vector addresses.

Internal Data RAM. The Z89C00 has an internal 512 x

16-bit word data RAM organized as two banks of 256 x

16-bit words each, referred to as RAM0 and RAM1. Each

data RAM bank is addressed by three pointers, referred to

as Pn:0 (n = 0-2) for RAM0 and Pn:1 (n = 0-2) for RAM1. The

RAM addresses for RAM0 and RAM1 are arranged from

0-255 and 256-511, respectively. The address pointers,

which may be written to or read from, are 8-bit registers

connected to the lower byte of the internal 16-bit D-Bus

and are used to perform no overhead looping. Three

addressing modes are available to access the Data RAM:

register indirect, direct addressing, and short form direct.

These modes are discussed in detail later. The contents of

the RAM can be read or written in one machine cycle per

word without disturbing any internal registers or status

other than the RAM address pointer used for each RAM.

The contents of each RAM can be loaded simultaneously

into the X and Y inputs of the multiplier.

Registers. The Z89C00 has 12 internal registers and up to

an additional eight external registers. The external registers

are user definable for peripherals such as A/D or D/A or to

DMA or other addressing peripherals. External registers

are accessed in one machine cycle the same as internal

registers.

DC 4083-00

5