CS9236-CQ View Datasheet(PDF) - Cirrus Logic

Part Name

Description

Manufacturer

CS9236-CQ Datasheet PDF : 34 Pages

| |||

CS9236

CS9236 Clocks and Timing Generation

The CS9236 internal timing is derived from one of two pos-

sible sources; the part may be supplied a 16.9344 MHz Mas-

ter Clock signal from an external source, or the timing may be

generated using the on-chip oscillator circuit in conjunction

with an external 16.9344 MHz quartz crystal. When a Master

Clock signal is provided to the CS9236 from an external de-

vice, the Master Clock signal should be connected to the

CS9236 MCLK5I input pin and the XTAL3I input pin is

grounded. When the CS9236 internal timing is generated us-

ing the on-chip oscillator circuit, a 16.9344 MHz quartz crys-

tal is connected between the CS9236 XTAL3I input pin and

the XTALO output pin, and the MCLK5I input pin is ground-

ed. In this case, the XTALO output may also be used as a

384X master clock for the CS9236 digital audio output signal,

SOUT.

Power-Down Modes

The CS9236 provides a fully-static power-down mode of op-

eration. The power-down mode is initiated either by assertion

of the active-low PDN signal, or by gating off of the MCLK5I

input signal (via the CODEC DMCLK bit in CS4236B/7B/8B

applications). In the power-down mode of operation, clock

signals to virtually all of the CS9236 internal circuitry are gat-

ed off to minimize power consumption. The CS9236 device

is fully static, so all internal states and register values will be

retained during power-down, provided that power remains

applied to the device and that the RST signal remains inac-

tive. Power-down operation is terminated either by deasser-

tion of PDN or by gating back on the MCLK5I input signal.

The device will then resume normal operation.

Digital Audio Interface

The CS9236 provides a stereo 16-bit serial digital audio out-

put at a 44.1 ksample/s sampling rate. The CS9236 digital au-

dio output is compatible with the Crystal Semiconductor

CS4236B/37B/38B and CS4333 devices. The digital audio

interface consists of the digital audio output signal, SOUT,

and the associated left/right word clock output, LRCLK.

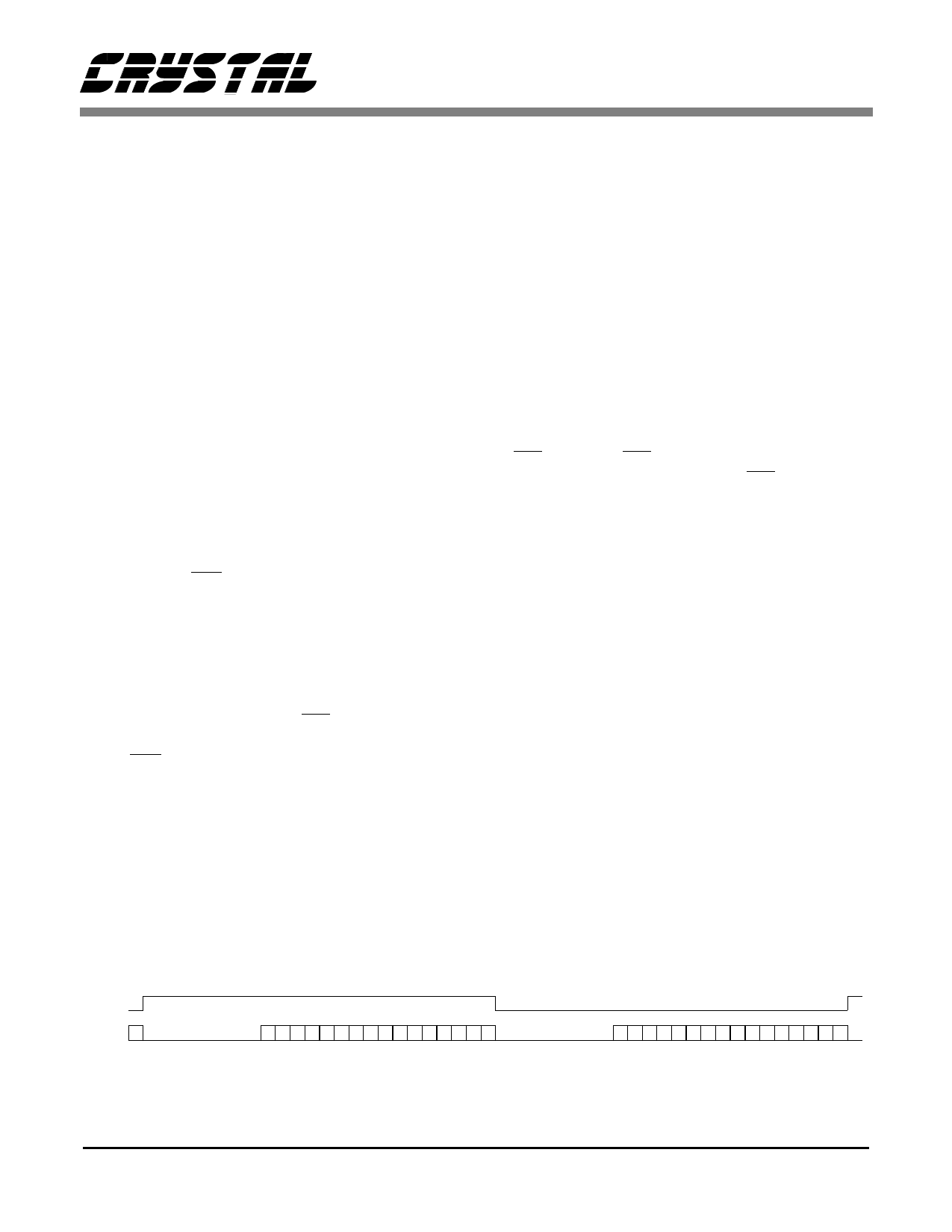

Transitions of the SOUT and LRCLK signals are synchro-

nous to the CS9236 crystal oscillator output clock, XTALO.

The relationship between the CS9236 SOUT data output and

the LRCLK clock output is indicated in Figure 4.

Reset

The CS9236 is initialized/reset to a known default state using

the RST signal. The RST signal should be applied at power-

on time to initialize the part. Minimum RST pulse width is

500 ns.

LRCLK

SOUT 0

8-bits

Left Channel

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

8-bits

Right Channel

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Figure 4. Digital Audio Port Format.

DS214PP11

9