M1025-1026 View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

M1025-1026 Datasheet PDF : 16 Pages

| |||

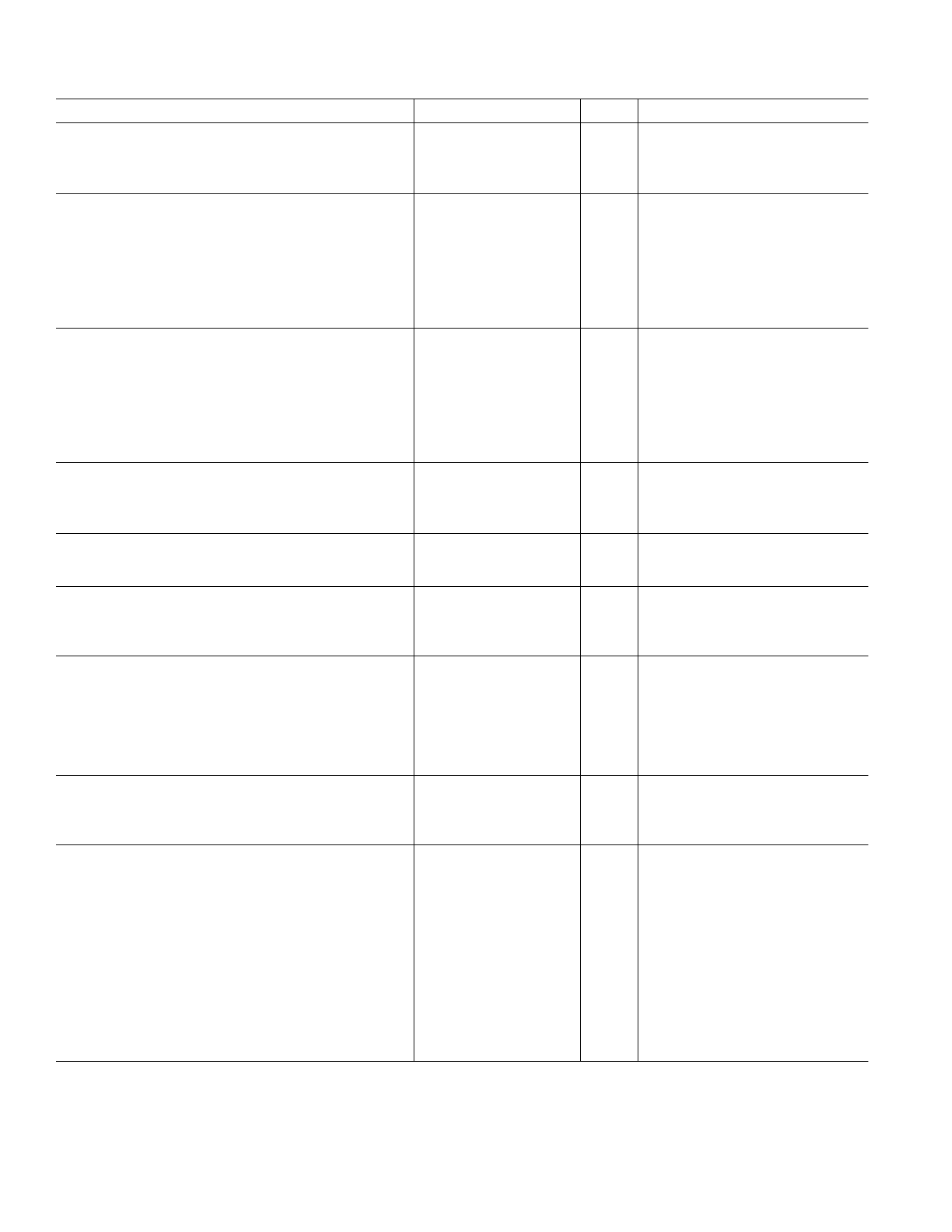

ADM1025/ADM1025A–SPECIFICATIONS (TA = TMIN to TMAX, VCC = VMIN to VMAX, unless otherwise noted.)

Parameter

Min Typ Max Unit Test Conditions/Comments

POWER SUPPLY

Supply Voltage, VCC

Supply Current, ICC

3.0 3.30 5.5

V

(Note 1)

1.4

2.5

mA

Interface Inactive, ADC Active

32

500

µA

Standby Mode (Note 2)

TEMPERATURE-TO-DIGITAL CONVERTER

Internal Sensor Accuracy

Resolution

External Diode Sensor Accuracy

Resolution

Remote Sensor Source Current

±3

°C

1

°C

±5

°C

±3

°C

60°C ≤ TA ≤ 100°C; VCC = 3.3 V

1

°C

180

µA

High Level

11

µA

Low Level

ANALOG-TO-DIGITAL CONVERTER

(INCLUDING MUX AND ATTENUATORS)

Total Unadjusted Error, TUE

±2

Differential Nonlinearity, DNL

±1

Power Supply Sensitivity

±1

Conversion Time (Analog Input or Internal Temperature)

11.6

Conversion Time (External Temperature)

34.8

Input Resistance (2.5 V, 3.3 V, 5 V, 12 V, VCCPIN)

100 140 250

OPEN-DRAIN DIGITAL OUTPUT ADD/RST/INT/NTO

Output Low Voltage, VOL

High Level Output Leakage Current, IOH

RST Pulsewidth

0.4

0.1

1

20

45

%

(Note 3)

LSB

%/V

ms

(Note 4)

ms

(Note 4)

kΩ

V

IOUT = –6.0 mA; VCC = 3 V

µA

VOUT = VCC; VCC = 3 V

ms

OPEN-DRAIN SERIAL DATA BUS OUTPUT (SDA)

Output Low Voltage, VOL

High Level Output Leakage Current, IOH

SERIAL BUS DIGITAL INPUTS (SCL, SDA)

Input High Voltage, VIH

Input Low Voltage, VIL

Hysteresis

0.4

V

IOUT = –6.0 mA; VCC = 3 V

0.1

1

µA

VOUT = VCC

2.1

V

0.8

V

500

mV

DIGITAL INPUT LOGIC LEVELS

(ADD, VID0–VID4, NTI)5

VID0–3 Input Resistance

VID4 Input Resistance

Input High Voltage, VIH6

Input Low Voltage, VIL6

100

kΩ

ADM1025 Only

300

kΩ

ADM1025 Only

100

kΩ

ADM1025A

2.1

V

0.8

V

DIGITAL INPUT LEAKAGE CURRENT

Input High Current, IIH

Input Low Current, IIL

Input Capacitance, CIN

–1

1

5

µA

VIN = VCC

µA

VIN = 0

pF

SERIAL BUS TIMING

Clock Frequency, fSCLK

Glitch Immunity, tSW

Bus Free Time, tBUF

Start Setup Time, tSU:STA

Start Hold Time, tHD:STA

Stop Condition Setup Time tSU:STO

SCL Low Time, tLOW

SCL High Time, tHIGH

SCL, SDA Rise Time, tR

SCL, SDA Fall Time, tF

Data Setup Time, tSU:DAT

Data Hold Time, tHD:DAT

50

1.3

600

600

600

1.3

0.6

100

300

400

kHz

See Figure 1

ns

See Figure 1

µs

See Figure 1

ns

See Figure 1

ns

See Figure 1

ns

See Figure 1

µs

See Figure 1

µs

See Figure 1

300

ns

See Figure 1

300

ns

See Figure 1

ns

See Figure 1

ns

See Figure 1

NOTES

1All voltages are measured with respect to GND, unless otherwise specified.

2Typicals are at TA = 25°C and represent most likely parametric norm. Shutdown current typ is measured with VCC = 3.3 V.

3TUE (Total Unadjusted Error) includes Offset, Gain and Linearity errors of the ADC, multiplexer and on-chip input attenuators, including an external series input

protection resistor value between zero and 1 kΩ.

4Total monitoring cycle time is nominally 114.4 ms. Monitoring Cycle consists of 6 Voltage + 1 Internal Temperature + 1 External Temperature readings.

5ADD is a three-state input that may be pulled high, low or left open-circuit.

6Timing specifications are tested at logic levels of VIL = 0.8 V for a falling edge and VIH = 2.2 V for a rising edge.

Specifications subject to change without notice.

–2–

REV. A