SSD1818 View Datasheet(PDF) - Unspecified

Part Name

Description

Manufacturer

SSD1818 Datasheet PDF : 44 Pages

| |||

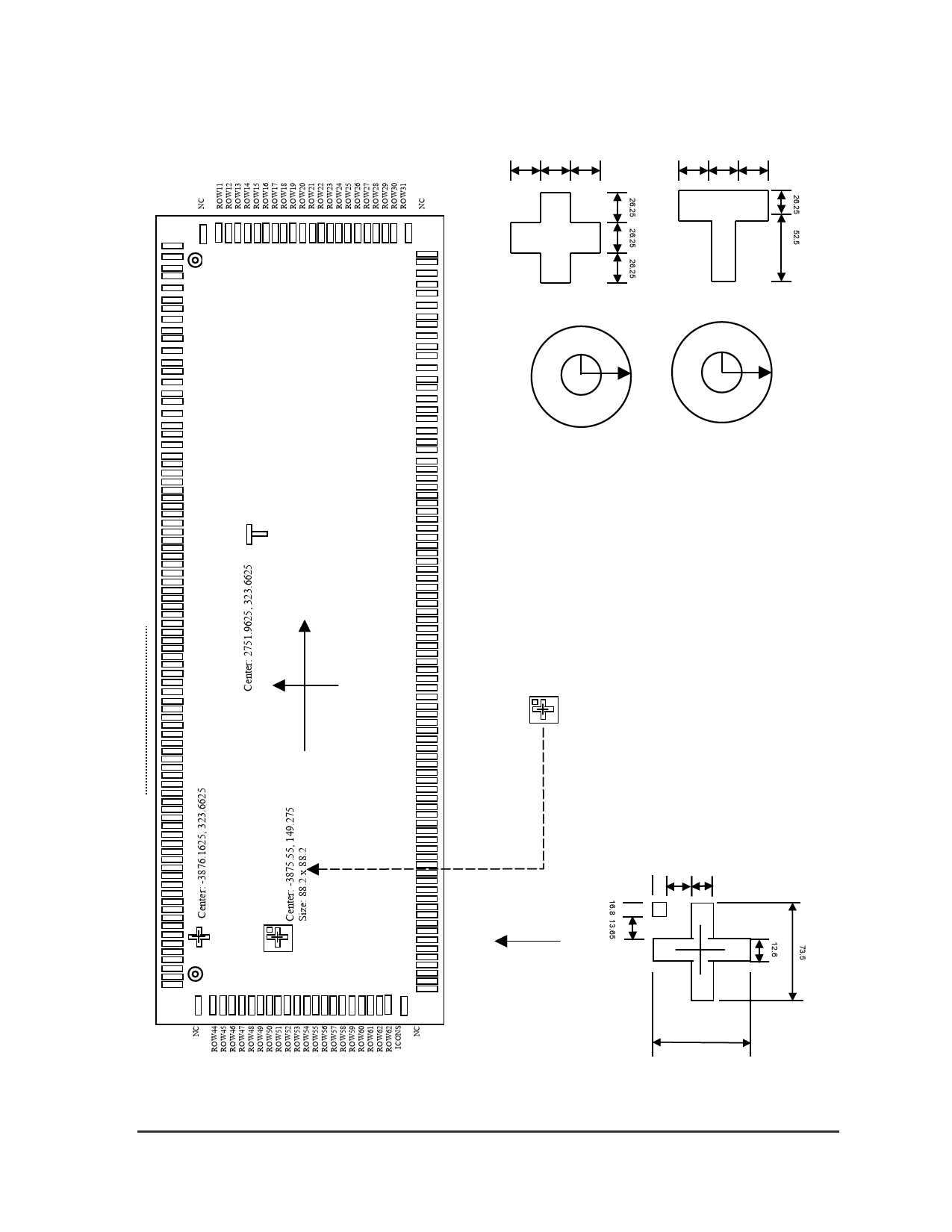

DIE PAD ARRANGEMENT

26.25 26.25 26.25

26.25 26.25 26.25

126

ROW10

ROW9

ROW8

ROW7

ROW6

ROW5

ROW4

ROW3

ROW2

ROW1

ROW0

ICONS

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

125

(2755.725, 237.475)

SEG92

SEG93

SEG94

SEG95

SEG96

SEG97

SEG98

SEG99

SEG100

SEG101

SEG102

SEG103

ROW32

ROW33

ROW34

ROW35

ROW36

ROW37

ROW38

ROW39

ROW40

ROW41

ROW42

ROW43

(-3878.7, 237.475)

254 255

277

104 103

T2

T1

T0

/SPI

VSS

IRS

VDD

C1

VSS

C0

VDD

P/S

C68/80

VSS

CLS

M/S

VDD

T3

VL6

VL6

VL6

VL5

VL5

VL5

VL4

VL4

VL4

VEE

VL3

VL3

VL3

VL2

VL2

VL2

VEE

C4N

C4N

C4N

C2P

C2P

C2P

C2N

C2N

C2N

VEE

C1N

C1N

C1N

C1P

C1P

C1P

C3N

C3N

C3N

TEST2

VEE

VEE

VEE

VEE

VEE

VEE

VSS1

VSS1

VSS1

VSS1

VSS1

VSS

VSS

VSS

TEST1

TEST0

VDD

VDD

VDD

VDD

VDD

VDD

VDD

D7

D6

D5

D4

D3

D2

D1

D0

VDD

E/RD

R/W

VSS

D/C

VEE

VEE

/RES

VDD

CS2

/CS1

VSS

276

/DOF

1 CL

M

MSTAT

X

Center (-3876.1625, 323.6625)

X

Center (2751.9625, 323.6625)

8.75 35

X

(-3878.7, 237.475)

8.75 35

X

(2755.725, 237.475)

Note:

1.

2.

The gold bumps face up in this

diagram

All dimensions in µm and (0,0) is

the center of the chip

Die Size:

Die Thickness:

Bump Pitch:

Bump Height:

Tolerance

8.66 mm X 1.48 mm

675 +/- 25 um

60 um [Min]

Nominal 18 um

< 4 um within die

< 8 um within lot

Gold Bump Alignment Mark

This alignment mark contains gold bump

for IC bumping process alignment and IC

identifications. No conductive tracks

should be laid underneath this mark to

avoid short circuit.

16.8 13.65 12.6

PIN #1

Center (3875.55, 149.275)

SSD1818 Series

Rev 1.2

08/2002

Figure 2 – SSD1818 Pin Assignment

73.5

4

SOLOMON