MPC2605ZP66R View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

MPC2605ZP66R Datasheet PDF : 30 Pages

| |||

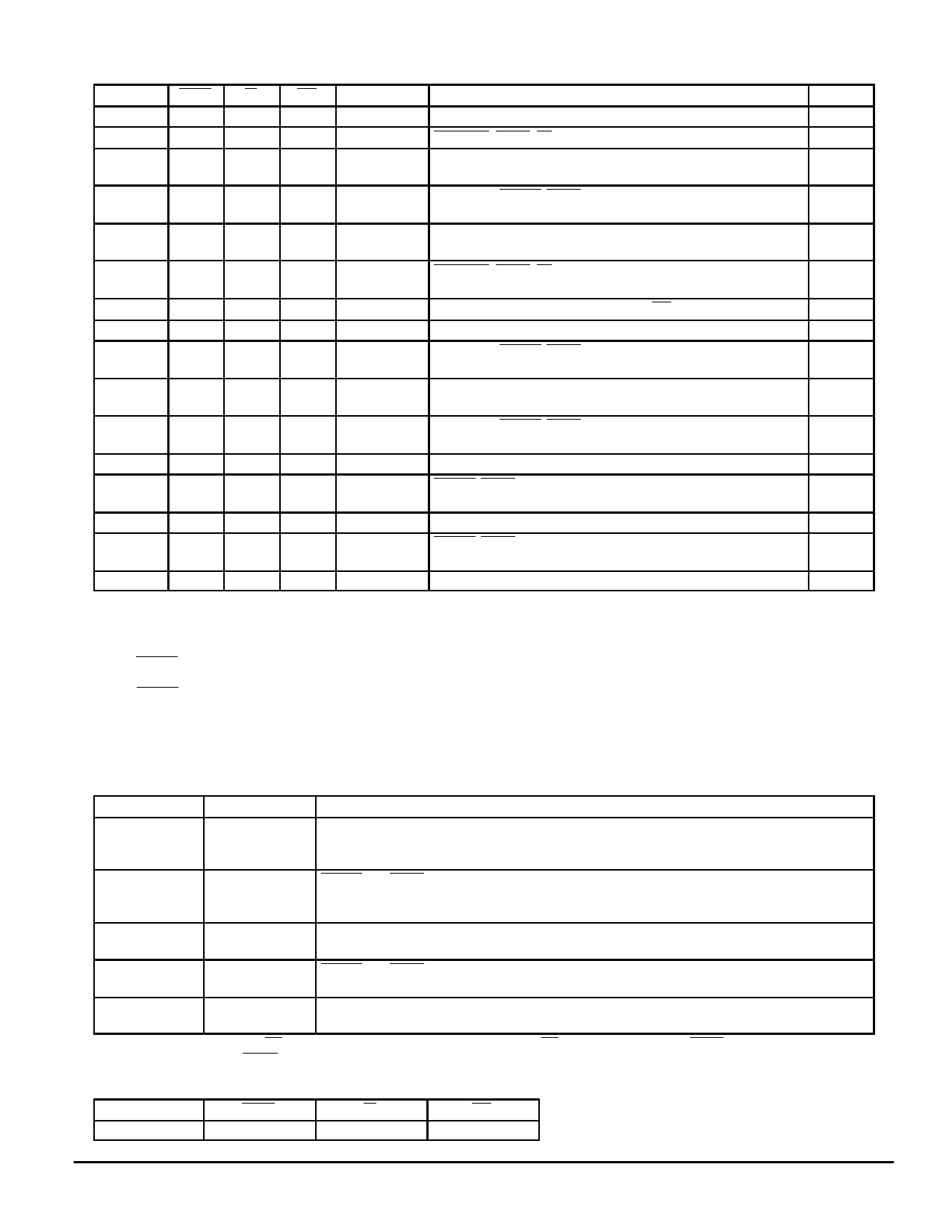

MPC2605 RESPONSE TO 60X TRANSFER ATTRIBUTES

TT0 – TT4 TBST

CI

WT

Tag Status

MPC2605 Response

Notes

X1X10

0

1

X

Miss

Line–fill (processor read miss)

1, 2, 3

X1X10

0

1

X

Hit

L2 CLAIM, AACK, TA (processor read hit)

4

X1010

1

0

X

Hit Clean Paradox — Invalidate the line (processor n–cacheable read hit

clean line)

X1010

1

0

X

Hit Dirty Paradox — ARTRY, L2 BR, then write back data, invalidate the line

(processor n–cacheable read hit dirty line)

00110

0

1

X

Miss

Line–fill except right after a snoop hit to processor (processor write 1, 3, 5, 6

miss)

00110

0

1

1

Hit

L2 CLAIM, AACK, TA except after a snoop hit to processor

5, 6

(processor write hit)

00X10

X

1

0

Hit Clean Cache update (processor write through WT hit clean)

00110

0

1

0

Hit Dirty Cache update, clear dirty bit

00010

1

1

0

Hit Dirty Paradox — ARTRY, L2 BR, write back data, keep valid, clear dirty

bit

X0010

1

0

X

Hit Clean Paradox — Invalidate the line (processor n–cacheable write hit

clean line)

X0010

1

0

X

Hit Dirty Paradox — ARTRY, L2 BR, then write back data, invalidate the line

(processor n–cacheable SB write hit dirty line)

00100

X

X

X

Hit Clean Invalidate tag (flush block address–only)

00100

X

X

X

Hit Dirty ARTRY, L2 BR, write back data, invalidate tag (flush block

address–only)

00000

X

X

X

Hit Clean No action (clean block address–only)

00000

X

X

X

Hit Dirty ARTRY, L2 BR, write back data, reset dirty bit (clean block

address–only)

01100

X

X

X

Hit

Invalidate tag (kill block address–only)

NOTES:

1. If a line fill is going to replace a dirty line and the cast out buffer (COB) is full, the line fill will be cancelled. (Unless the line fill is a write which

hits in the COB. In this case, the line fill will occur.)

2. If a burst read misses the cache but hits the COB, the MPC2605 will supply the data from the COB, but not perform a line fill.

3. If ARTRY is asserted during a line fill to replace a dirty line, the line fill will be cancelled, the to–be–replaced line will recover its old tag (valid,

dirty, tag field), and the COB goes back to an invalid condition, even if the line fill is a burst write to the line in the COB.

4. If ARTRY is asserted during a read hit, the MPC2605 will abort the process.

5. If a processor burst write occurs right after a snoop write that was a cache hit, the MPC2605 will invalidate the line. If the snoop was a cache

miss, the MPC2605 will not perform a write allocate.

6. If a processor burst write occurs right after a snoop read that was a cache hit, the MPC2605 will update the cache and clear the dirty bit.

If the snoop was a cache miss, the MPC2605 will perform a write allocate.

MPC2605 RESPONSE TO CHIPSET TRANSFER ATTRIBUTES

TT0 – TT4

Tag Status

MPC2605 Response

00100

X0010

X1110

Hit Clean

Invalidate line

00100

X0010

X1110

Hit Dirty

ARTRY and L2 BR write back data, invalidate line (see Note)

00000

X1010

Hit Clean

No action

00000

X1010

Hit Dirty

ARTRY and L2 BR, write back data, reset dirty bit (see Note)

0110X

00110

Hit

Invalidate (kill block)

NOTE: In all snoop push cases, BR is sampled the cycle after the ARTRY window. If BR is asserted in this cycle, L2 BR will be immediately negated

and an assertion of L2 BG will be ignored.

TRANSFER ATTRIBUTES GENERATED FOR L2 COPYBACK

TT0 – TT4

TBST

CI

WT

00010

0

1

1

MOTOROLA

MPC2605

9